Other Parts Discussed in Thread: PGA280

Hi.

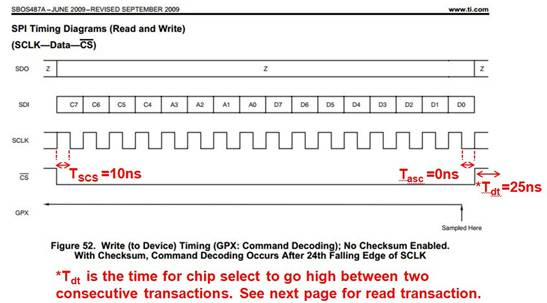

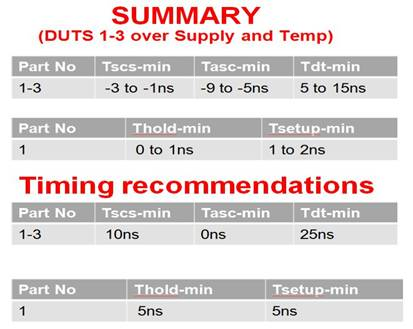

I have been unable to find much information on the SPI timing of the PGA280.

I have found only two statements in the datasheet. first is max SPIclk is 10MHz, and data is latched when SPI goes low.

Where can I find information about setup and hold time on the data in, and delay on data out. I there any requirement regarding the CS on delay or similar.

Regards Martin