Hello all:

I'm new in the OP amp system design. And I read many TI application note but still confused.

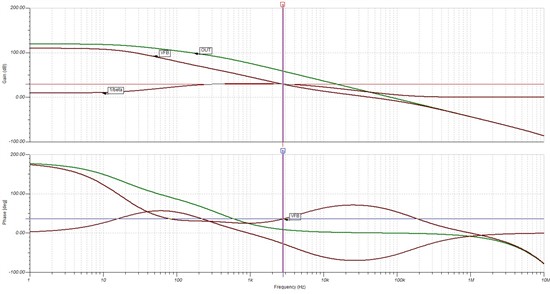

I have some OP amp stabilize issues in my design. I use DAC and OP amp in my system. And OP amp with a 22uF ceramic cap.

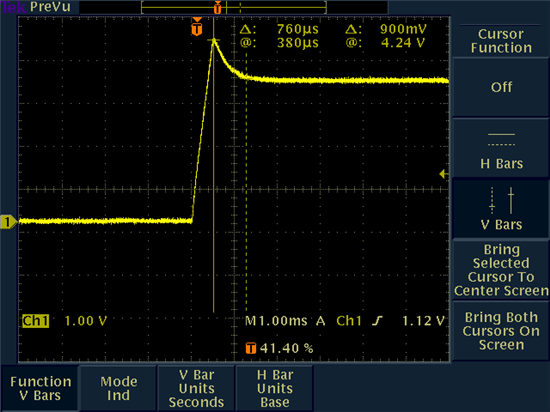

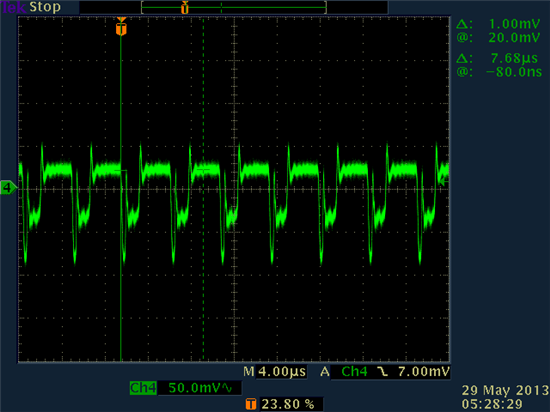

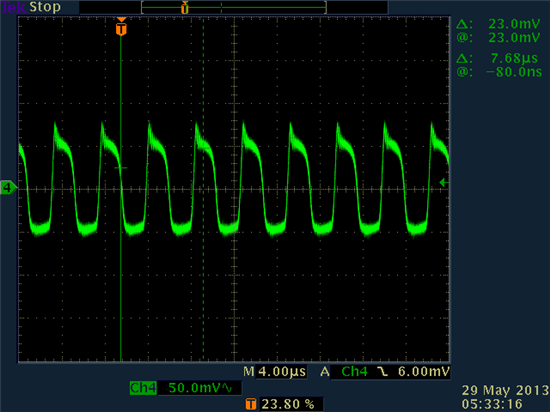

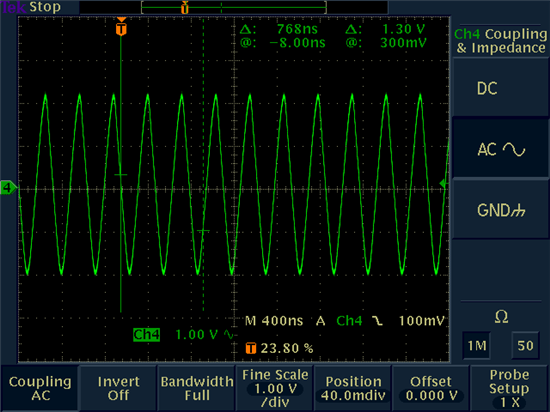

I use this op amp as non-inverting amplifier. And the schematic as attached pic. I found that Vout is oscillate and the current consume by OPA552 was very high(abt. 150mA).

I know that I can use OPA552 as Gain<5. Does this issues being solved if I change my op to OPA551? Or how do I stabilize this circuit? Thanks!