Hello,

I've just got boards fresh from factory using LMV7272 comparators. Two of them behave strangely. More accurately, I've something I don't understand at the positive input:

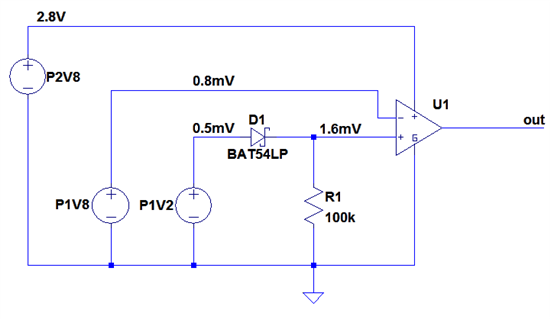

I'm using them to check that a 1.2V supply minus 0.2V is always lesser than a 1.8V supply. To get the 0.2V offset I'm using a schottky diode in series with the 1.2V supply, with a 100k pull down to minimize current losses.

At startup, when the two supplies are shutdown I'm measuring at the anode a greater voltage than on the cathode:

Does someone has any clue? Thanks.