Other Parts Discussed in Thread: OPA847, LMH6629, TINA-TI, OPA657

Dear all

I am designing Transimpedance (TIA) amplifier with OPA847, choosening because of its high GBW and smallest input voltage noise.

However, I got a problem about "stability".

Given by the feedback theory and simulation results putting a small feedback capacitor in parallel with feedback resistor should making the TIA more stable (at the cost of the lower bandwidth).

However, once the feedback is larger than certain value (For example 1.1 pF when feedback resister is 1.8k), the system starts oscillating. If I reduce the value feedback capacitor, it start ringing.

I found someone else also get this problem. in http://e2e.ti.com/support/amplifiers/high_speed_amplifiers/f/10/t/38799.aspx

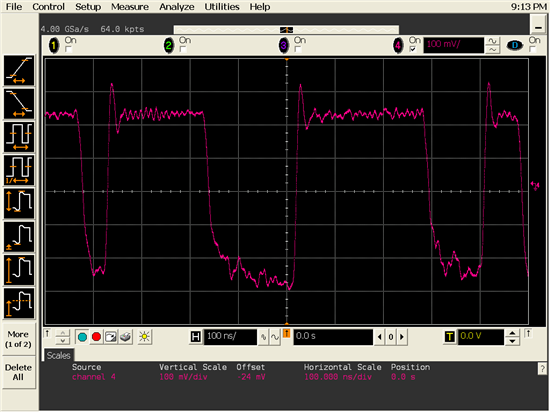

Here I attached two screen shot of my TIA. First one with big Cf, the system becomes unstable. Second with small feedback resistor, the system starts overshot.