Other Parts Discussed in Thread: OPA376

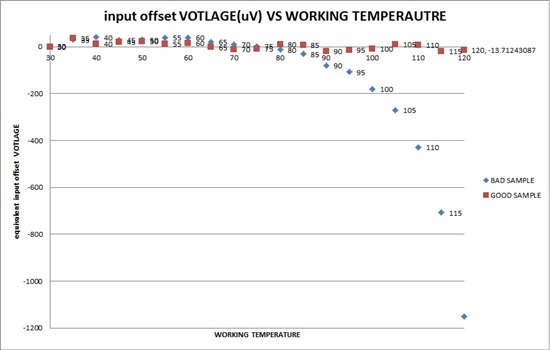

We use OPA376AIDCK as PCB trace current sense amplifier; the diagram is like below; we tried several samples and found some of them show very large equivalent input offset voltage under high working temperature like between 100'c and 125'c; the equivalent input offset voltage could be as high as 3mV(the higher the working temperature, the larger the equivalent input offset voltage)!!! while with working temperature below 100'c, the equivalent input offset voltage is very low; We did the test with DC input signal VS1=-6mV and no OSC was found on output by the way;

According to OPA376AIDCK's datasheet, the total equivalent offset voltage over Vsupply, working temperature range(25'c-125'c) and Vcm should be less than 0.3mV; while the test result is really bad for some samples;