Other Parts Discussed in Thread: OPA192

Dear support team

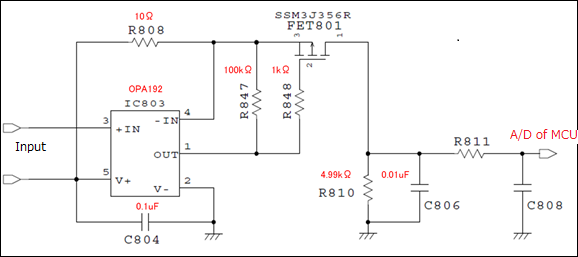

My customer is going to design the V-I conversion circuit using OPA192.

I want to confirm whether this circuit do not oscillate it, but simulation does not go well.

Could you advise it? (Please see attached file)

◆Condition

・They use OPA192 for current detection circuit of the high side

・Supply voltage:12V

・Common mode voltage:12V

・Gain:499

・Shunt resister:0.5mΩ

Regards

Tomohiro Nagasawa