Hello,

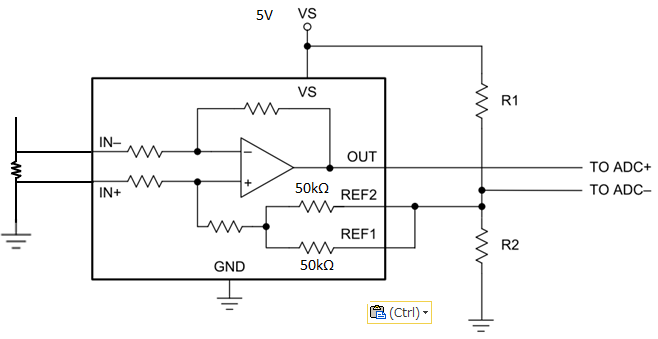

Customer is considering to use INA240A1 (20V/V) or INA240A2 (50V/V) with following figure.

This circuit use ADC- and ADC+ (differential ADC) so voltage change (error) of REF1/REF2 terminal will be cancelled so order of R1 and R2 should not be important, but customer wants to know the error of REF input voltage.

Datasheet has internal REF1 and REF2 value (50k ohm), but doesn’t explain internal input and feedback resistor value. So we can’t calculate the reference error caused by internal impedance and R1/R2

Please advise value of internal resistor or maximum leak current of REF1/REF2 terminal (INA240A1 and INA240A1) in case of above usage.

Best Regards.