Other Parts Discussed in Thread: TINA-TI, , THS3202

Tool/software: TINA-TI or Spice Models

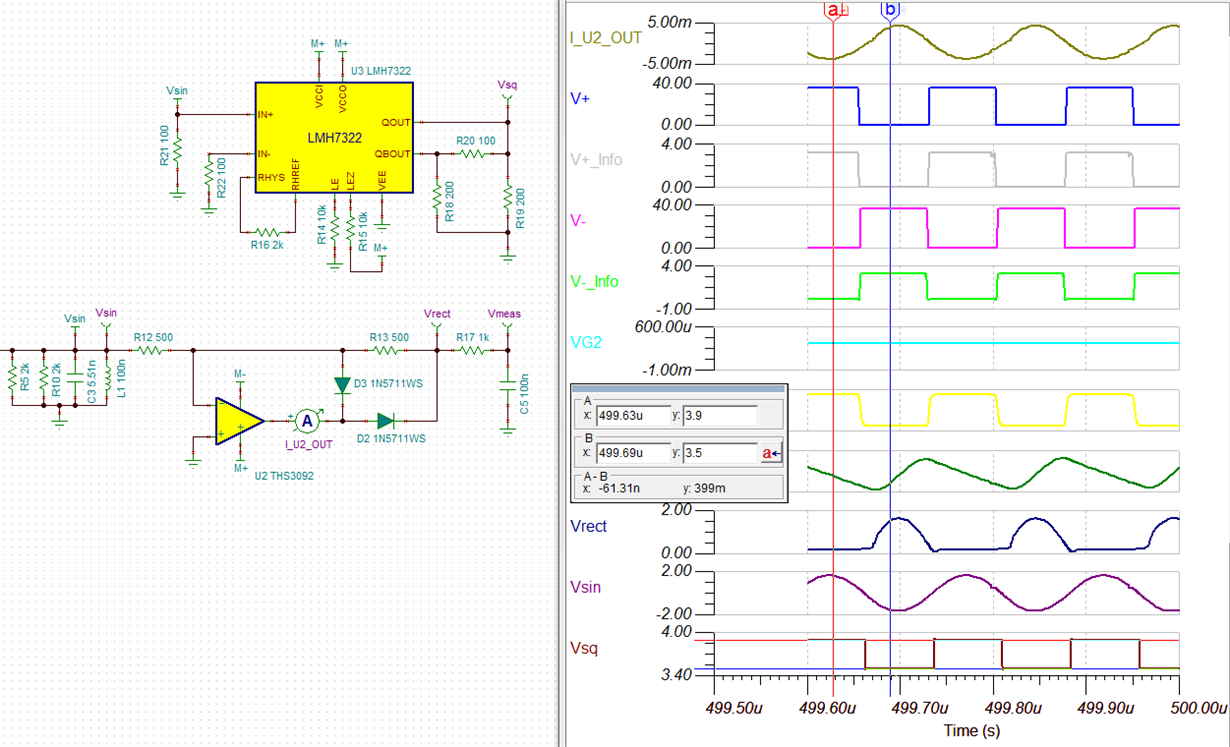

I have designed my board around LMH7322 with following schematic

But output of board is not changing. Now I suspect that latch is not enabled. Because LE and LEB connections are swapped in EVAL schematic.

Simulation also works if both LE and LEB are connected to ground but on board situation remains the same and we don't get the output.

Please confirm the issue if there is a problem with spice model supplied. Will it work if I swap the connection of LE and LEB.