Other Parts Discussed in Thread: INA303, OPA835, TIDA-00778, TIDA-00913

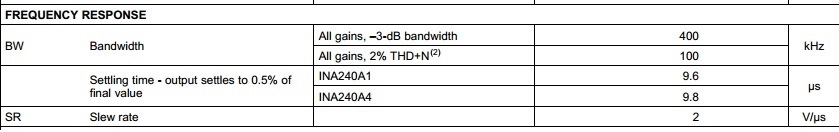

Logically table below could be interpreted as a range A1-A4 or only that A1 and A4 device have 9.6us, 9.8us respectively 0.5% of final value.

Then what is the settling time of A2 device, it seems to be roughly 1.5us on the scope?

Thanks!