Other Parts Discussed in Thread: TLV906X, OPA316

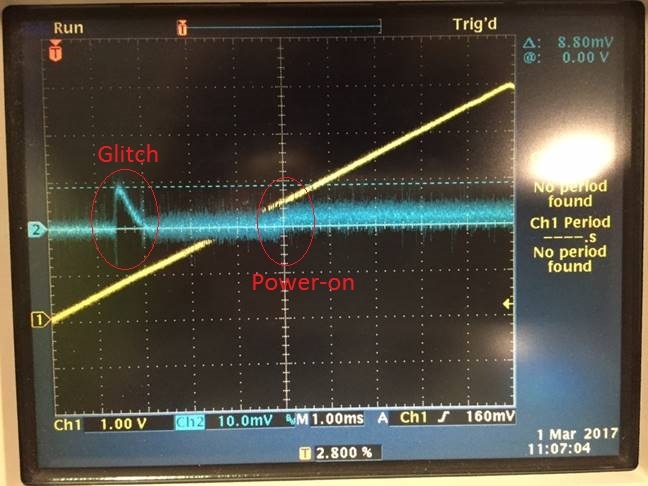

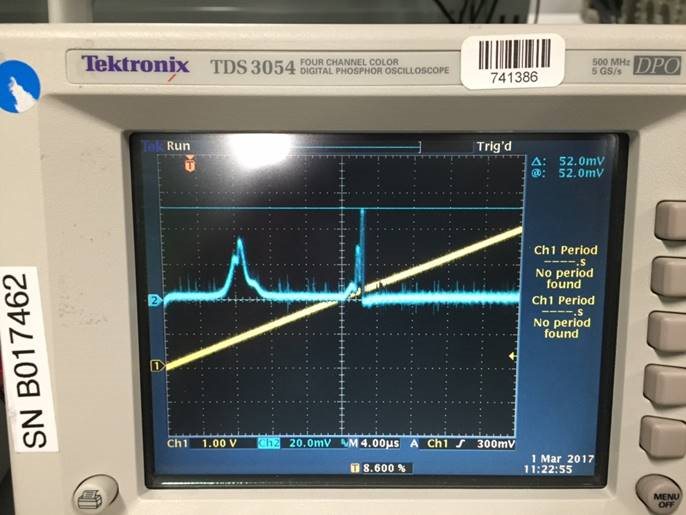

We have a design to restrict the current consumption of the TLV906x devices during inactive state. For this we plan to switch the power OFF when the signal conditioning is not to be done. The question is: What is the timing requirement on the power supply when ramped to 3.3V after which the OUT signal can be sampled by an ADC?

Is this parameter specified in the data sheet?