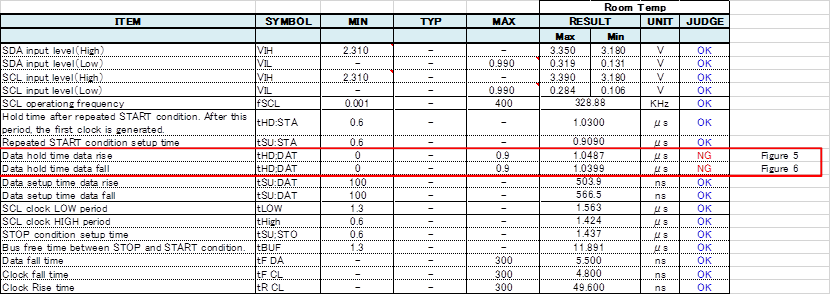

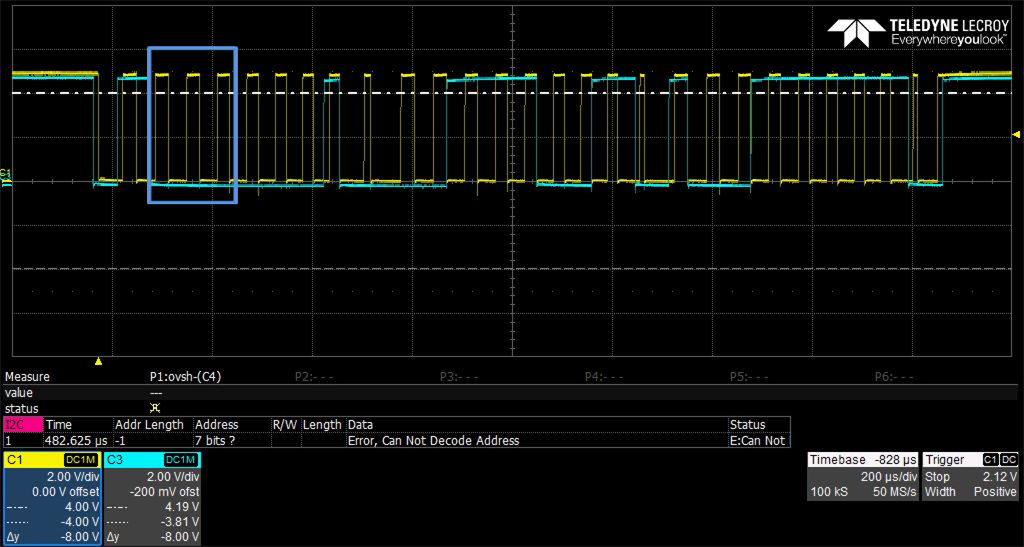

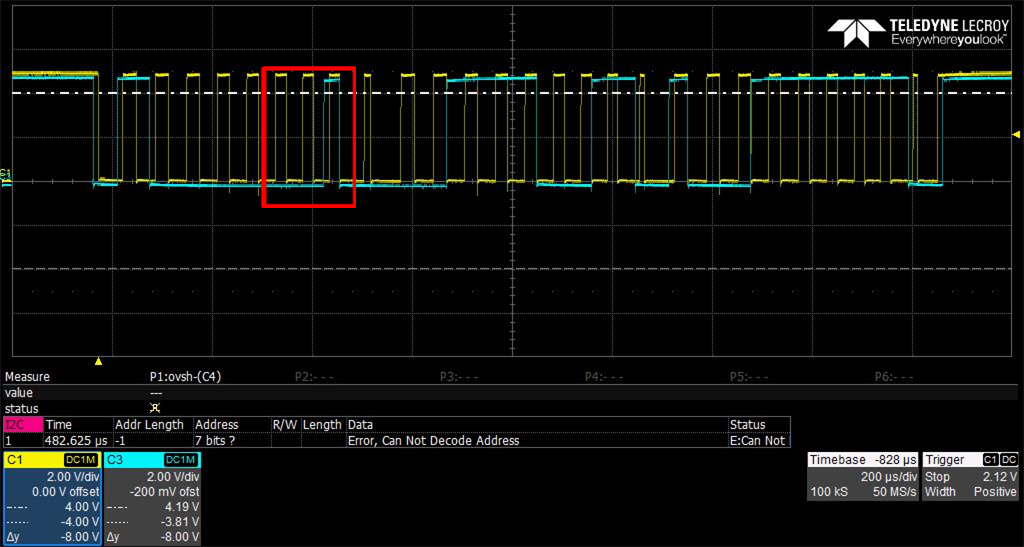

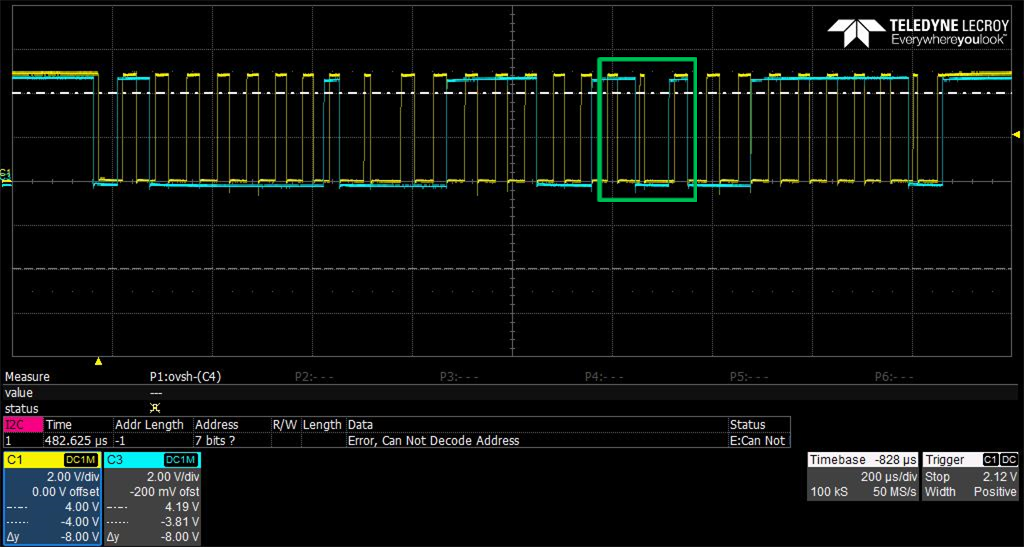

On the customer evaluating INA219B, I2C Data hold time is over the definition range.

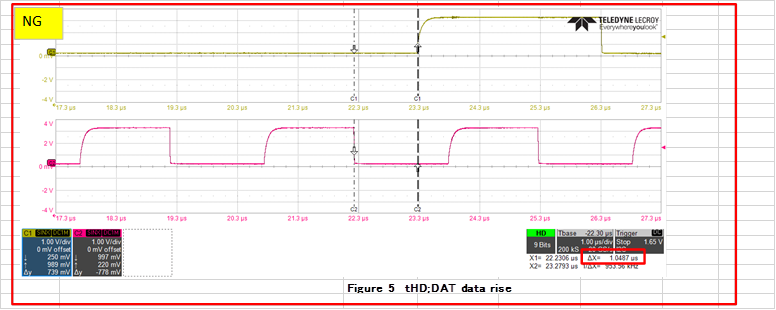

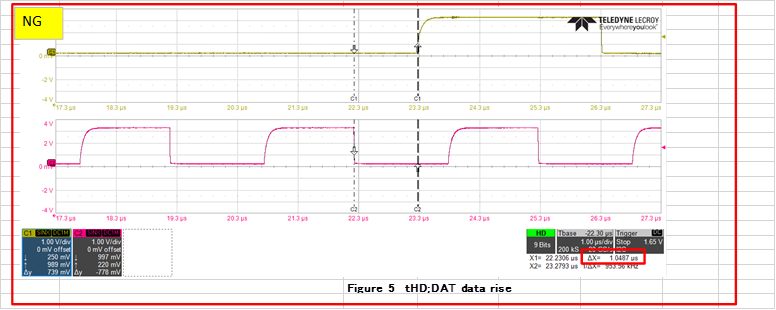

⇒Required 900ns_max at Fast Mode (Datasheet page-6), but below test results are near 1000ns.

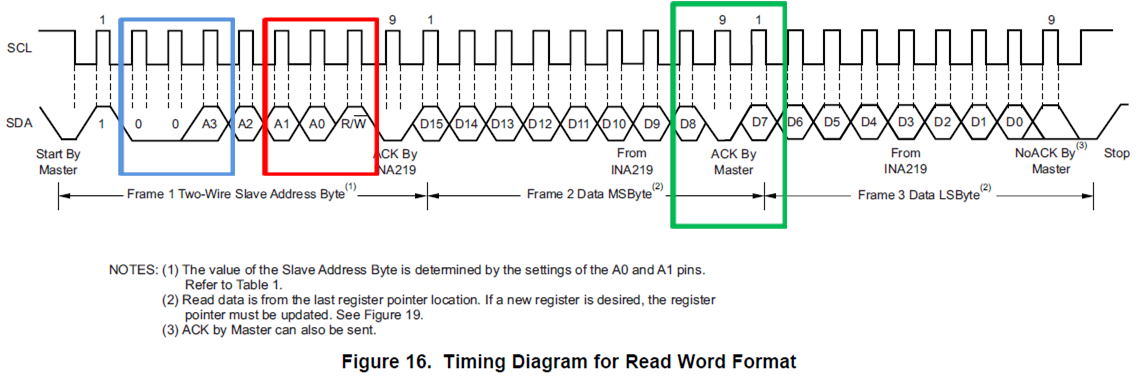

I think that test results should keep definition range, but tHD spec is depend on fSCL spec.

(Foe example; If in the case of fSCK:340kHz, tHD range will be ease)

Is it correct? If correct, please let me know about the relation for fSCL and tHD spec.

Best regards,

Satoshi