Other Parts Discussed in Thread: ADS8329

Hi

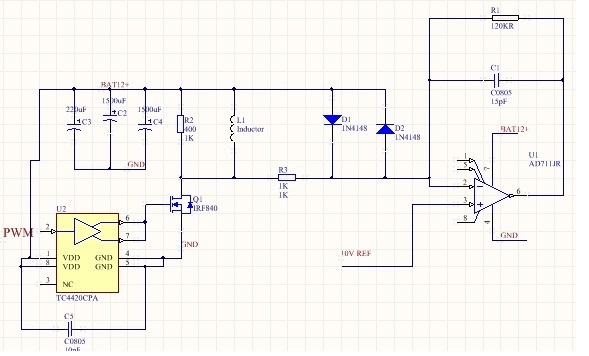

I want make pcb for below schematic..in this schematic PWM DRIVE Q1 SO L1 draw 3A .U1 (OP AMP) INVERTING INPUT FEED FROM R3..

BECAUSE L1 CONSUME HIGH CURRENT I WANT SEPARATE L1 GROUND PLANE FROM PRECISION CIRCUITS GROUND PLANE .

BUT MY QUESTION IS : HOW CONNECT R3 TO U1 (OP AMP PIN 2) OVER GROUND PLANE GAP?? IN WHOLE PCB TIPS RECOMMENDED NOT PASS TRACE OVER GROUND PLANE GAP !! ON THE OTHER HAND RECOMMENDED PARTITIONING GROUND PLANE FOR NOISE IMMUNITY .

I DRAW A LAYOUT AND PUT HERE FOR SAMPLE .

IN THIS PCB LAYOUT I CONNECT TOW GND PLANE WITH A BRIDGE AND CONNECT R3 TO U1 OVER THIS BRIDGE.

THIS MANNER IS TRUE??

THANKS.

SINCERELY .