Other Parts Discussed in Thread: TINA-TI, TLV3501

Tool/software: TINA-TI or Spice Models

Hi Folks,

I am very new to the analogue world (have spent 40+ years in the digital world !) so please be gentle if what I am about to ask is just nonsense !

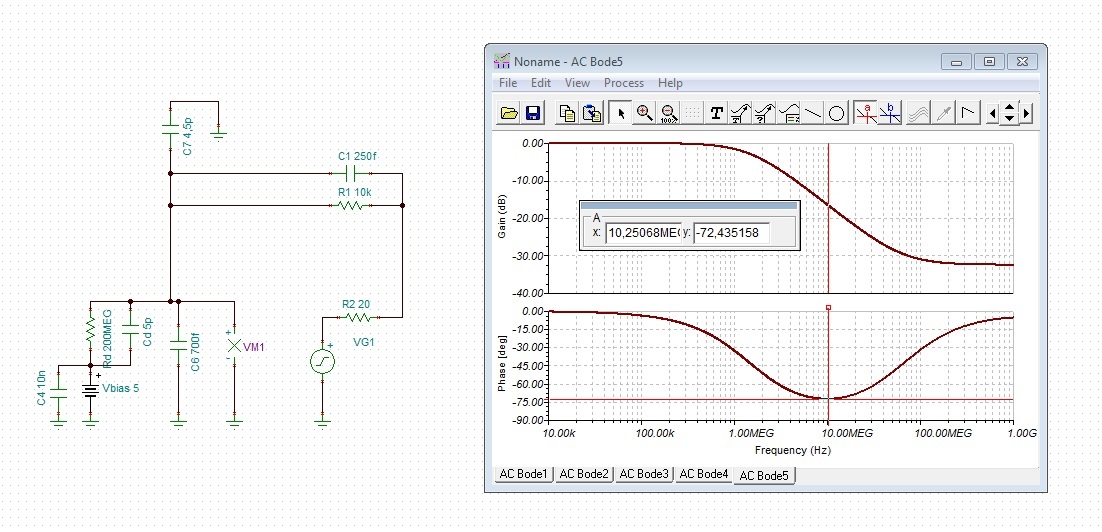

I attach a Tina-Ti example file for a 100Hhz Transimpedance amplifier that I have run an AC Analysis on and embedded the Gain/Phase Plot I get.

From a stability point of view I am being told that the phase margin is the difference between the phase at 0dB gain and -180 degrees. The plot shows the phase going from 0 to over 360 before

the gain reaches 0dB. Also I assume that as the phase approaches -180 just as the gain begins to roll-off that this would be a point of instability ?

In essence .... do these curves not prove that this circuit is inherently unstable ?