There is an issue with the INA180 (possibly other models in the same family when directly connected to the NXP 5168/5169 ZigBee SOC solution ADC2 pin (VREF/ADC2) in that a 30-100Khz saw-tooth waveform of a magnitude equal to ~ the difference between VIN+ and VIN- (Input pins across which the sense resistor is placed in a high side application (low side unchecked)) multiplied by the gain of the device. (the relationship is linear but may not be exactly 1:1 some losses are observed)

The oscillation is frequency and magnitude related to the difference across VIN+ and VIN- , the the relationship is not fully understood but appears to be 30Khz + some additional frequency giving ~ 100Khz at 1v difference on the inputs divided by the device gain) i.e on a 20 x gain device at 1 amp load with a 0.05Ohm resistor the amplitude is 780-900mV at frequency of ~ 100Khz

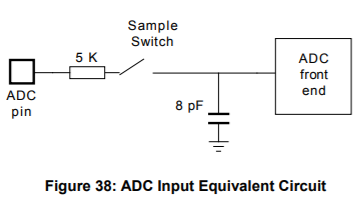

This can be mitigated by the inclusion of a 15K 1/4W (in this case) resistor between the output from the INA180 and the NXP5168/5169 ADC2/VREF pin (other values have not been tested)

If anyone else is able to verify this it would be appreciated and thoughts on the cause also welcome, by the looks it seems to be a sympathetic R/C network of some description.