Other Parts Discussed in Thread: TINA-TI,

Tool/software: TINA-TI or Spice Models

How do you plot CMRR of INA333 like the one shown in the Reference Design ?

Thanks

Pulin

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Pulin,

To test the CMRR of an instrumentation amplifier, you apply an AC test signal common to both of its inputs and measure the output. To refer back to the input, the output must be divided by INA gain. For example, if the INA is set up for G=1000 you must divide the output by 1000, and so on. I've attached a test circuit you can use for reference.

Best regards,

Ian Williams

Applications Engineer/SPICE Model Developer

Precision Amplifiers

Hi Ian,

Thank you for the explanation.

In an attempt to replicate the CMRR curve from the datasheet of the device, page 10, I set Vs+ to 5V, Vref to midsupply (2.5V) and Vs- to ground.

Simulating your reference circuit with above conditions for Gain of 1000, the CMRR curves give 150dB at around 10 Hz whereas the datasheet predicts this around 110dB. Am I doing something wrong here?

What is the purpose of in series switch with gain setting resistor ?

Regards

Pulin

Hi Pulin,

There is currently a limitation in our INA SPICE model architecture related to CMRR. While the input-referred CMRR of an INA will eventually hit some maximum at high gain, as shown by Figure 19 in the INA333 data sheet, the model's will keep getting better and better as gain increases. That's the source of the discrepancy.

The purpose of the switch in series with the gain setting resistor is so that you can open the circuit for G=1. You can also achieve G=1 by keeping the switch closed and setting RG to a very high value like 1T.

As Kai mentioned, the Vcm of the circuit is also a concern. In the split-supply configuration I attached, Vcm = 0V which is mid-supply. If you change to a single-supply configuration where Vs=+5V, make sure to adjust your Vcm to +2.5V as well as your Vref.

Best regards,

Ian Williams

Hi Ian,

Thanks for the explanation. I have changed Vin(common mode voltage) to +2.5V. The AC CMRR response remained unchanged.

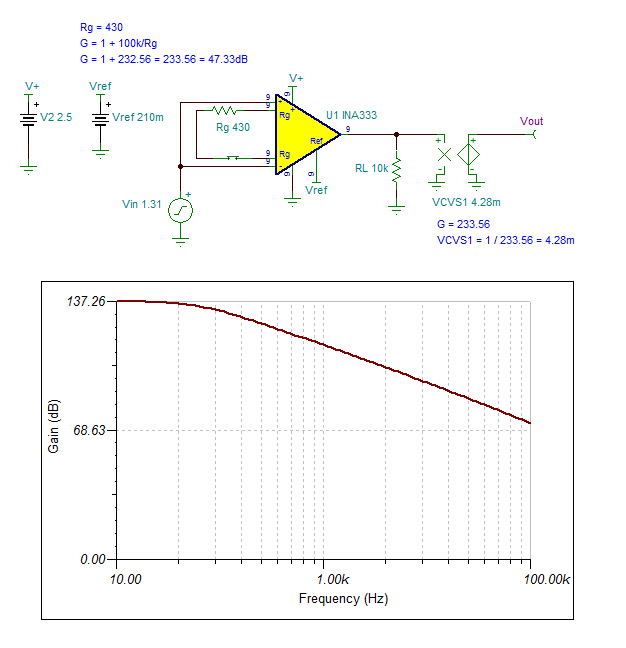

In my actual application, I have single supply configuration with Vref set to +210mV, and Vs = +2.5V with Rg set to 430 ohms representing Gain of 233.55(V/V).

The DC common mode voltage at the inputs is around 1.314V.

Provided there are limitations in the TINA model for INA333 like you have mentioned, is the representation of CMRR response below valid ?

Regards

Pulin

Hi Pulin,

Thank you for clarifying your application specifics. There are no problems with your power supply, Vcm, or Vref values.

Regarding the CMRR result, per Figure 19 of the data sheet the maximum CMRR of the INA333 is 115dB, which occurs at gains of 100V/V or greater. Since you are operating at a gain of 233.55V/V the CMRR will be 115dB.

By the way, when testing CMRR in simulation with G=233.55 you should set VCVS1 = 1 / 233.55 = 4.28m to refer the result back to the input. With our model we get a result of 137.26dB which is better than the real world.

We are working on several major fixes to our INA SPICE model architecture which will address this and other limitations, so I apologize for the inconvenience. Please let us know any other questions or concerns that you may have regarding your INA333 design and we'll be happy to help.

Best regards,

Ian Williams

Hi Ian,

Thank you for suggestion on VCVS1. It makes sense.

I was wondering if its possible to do a bench measurement of the CMRR with a function generator and oscilloscope. Where can I find guidelines to do so ?

I also have the INAEVM-MSOP8 evaluation board so I can use that too if necessary.

Regards

Pulin

Kai

Such a measurement may be 'simple' perhaps but 'simple' isn't the answer I was looking for. I was expecting to be pointed out to a specific TI application note. Enough time has been wasted to make INA333 spice model to produce sensible results.

Analog Devices on the other hand have published better guidelines for their devices. I recommend TI do the same or at least provide better than 'simple' guidance.

Hi Pulin,

I'm not an employee of TI. I apologize if you find my contributions "simple" and not to the point.

Kai

Hi Pulin,

Sorry for the delayed reply. We don't have any existing app note or other documentation that I'm aware with more specific guidelines for measuring INA CMRR. However, I have reached out to our characterization team to see what setup they use and I will reply when I have more information.

Best regards,

Ian Williams

Hi Pulin,

I got some tips from our characterization team. To measure CMRR vs. frequency, Kai's suggestion is correct in that you make the measurement the same way as shown in simulation: tie both inputs together, sweep a small input signal over frequency, measure the output transfer function, and divide by the INA gain to refer the result back to the input.

To get good results in the mid-to-high frequency range, make sure to do the following:

Measuring DC CMRR is much more involved. It requires a specialized, high-precision test setup, measurement techniques, and data processing in order to get accurate results.

Best regards,

Ian Williams

Measuring DC CMRR requires a two point measurement of the change of the input offset voltage vs the change of the input common-mode voltage:

CMRR=delta_Vcm / delta_Vos

Below please see the circuit configuration used for measuring DC CMRR for G=1 and the calculation of DC CMRR.

Since Vos=Vout, for Vin _diff=0 and G=1, CMRR=20*log(delta_Vcm/delta_Vos) = 20*log[5.3V/168uV] = 90dB