Dear Kai,

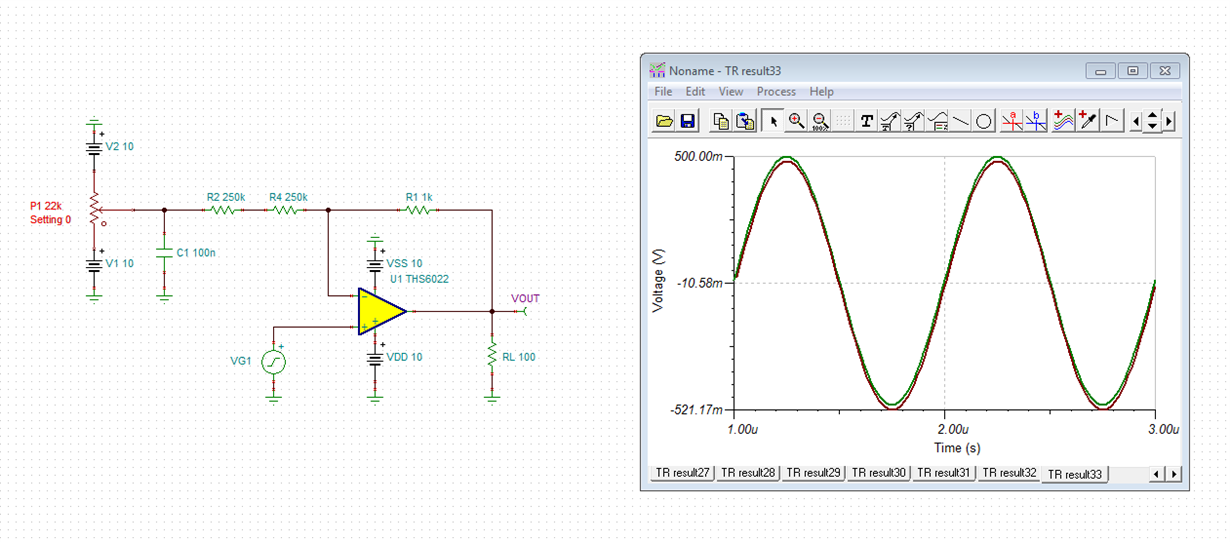

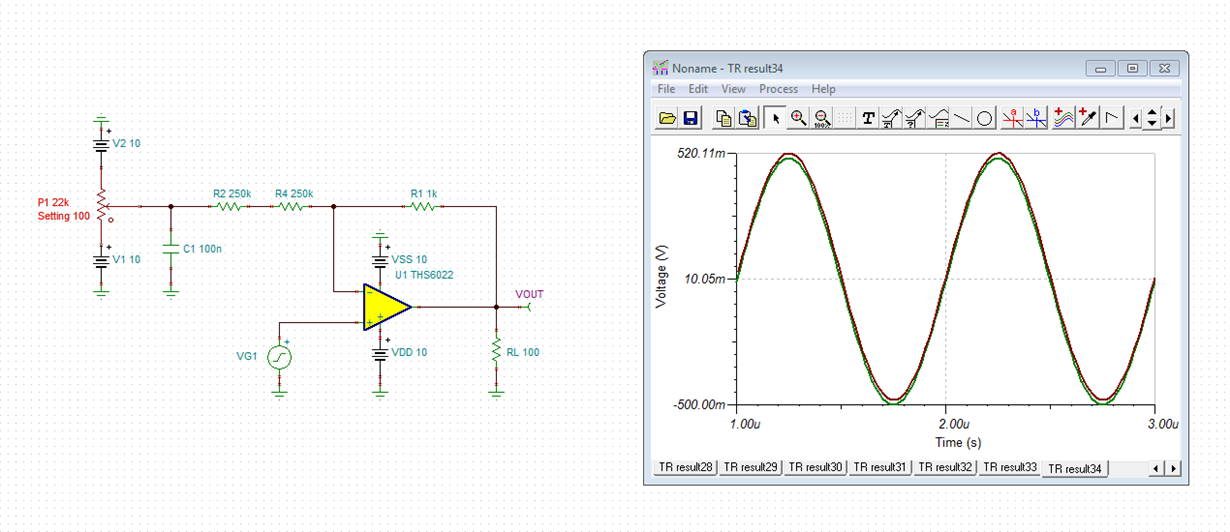

Thank you very much for this useful suggestion. I duplicated the scheme you provided. And I have achieved my function. By the way, there have about 20mV offset even though the IN+ is floating as shown in the Figure 2. Refering to the datasheet, the maximum offset should be about 5~7mV when gain=1. Do you know how to reduce this offset? Cause our project demand the offset is below 10mV.

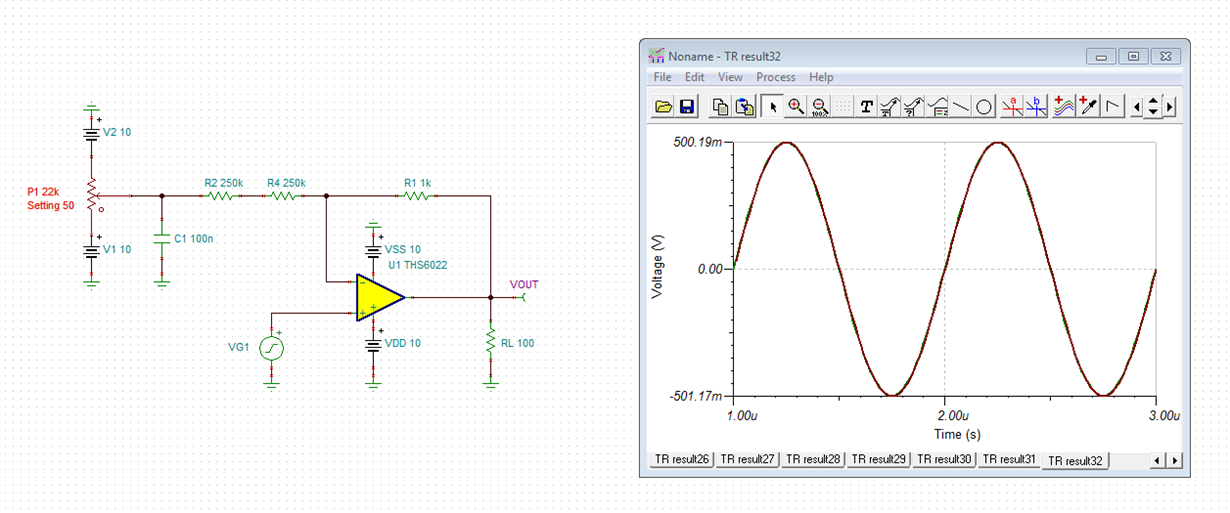

Figure 1: The function is exactly what I want

Figure 2: there exit about 20mV offset