Other Parts Discussed in Thread: IVC102

Dear Support,

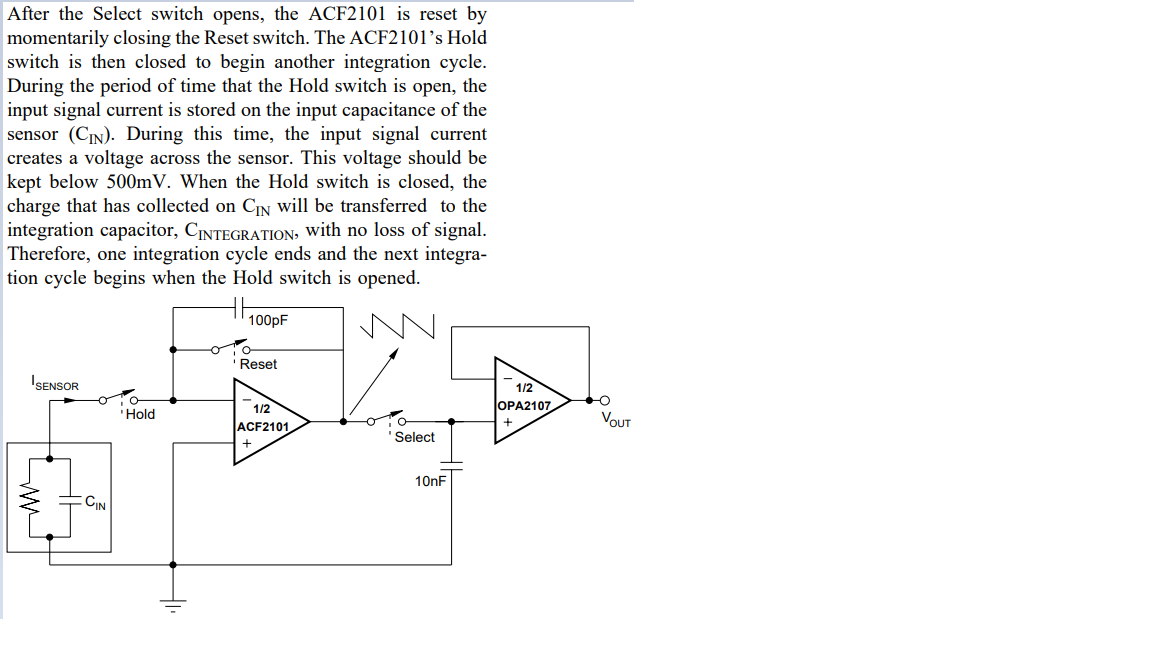

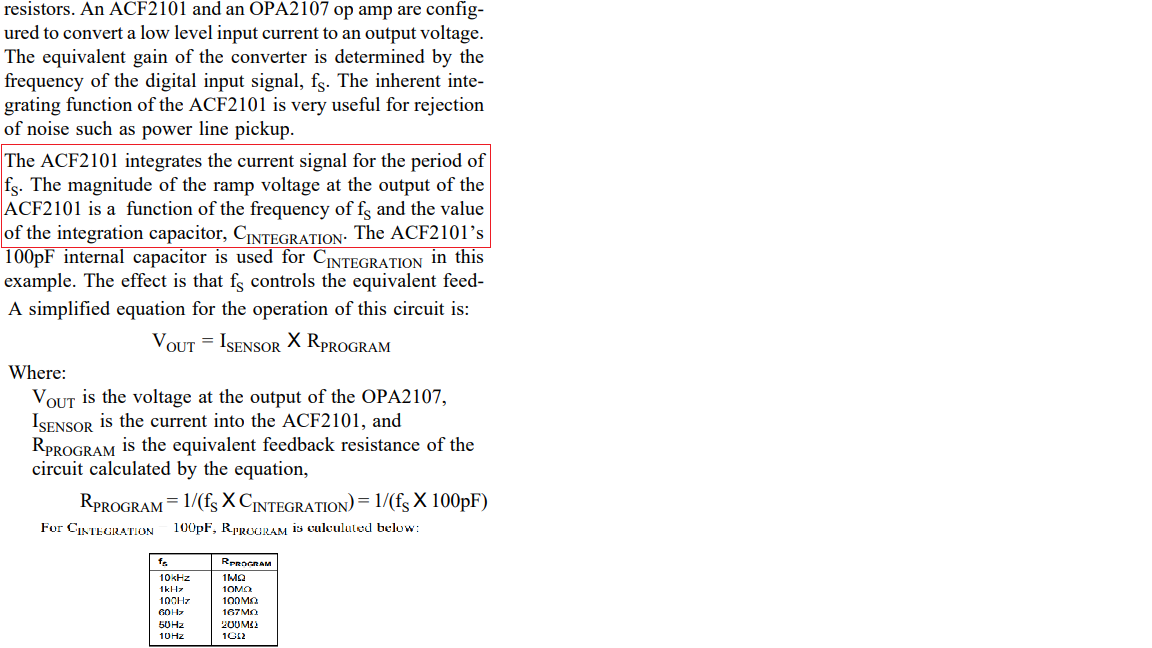

I am trying to configure the ACF2101 with current input. The power supply of the integrator is -15V, respectively +5V. I have applied a DC current of 0.1uA at the input from a current supply. I use the internal integration capacitor of 100pF and integrate for 16.7us. After the integration phase follows a hold phase and then a short reset phase (see attached timing diagramm). The phases are then repeated. The second integrator is never integrating (Hold is always on HI).

According to the formula in the datasheet I should get a voltage of 16.7mV at the end of the integration phase. However the output goes much higher (approximately 0.5V) and the integration curve looks weird (see attached oscilloscope screenshot).

I continuosly measured the voltage at the integrator’s input and this rises up to 0.5V, which is not desired – as I understood from the datasheet.

Color code of the signals on the screenshot:

Yellow: Hold signal

Purple: Output voltage, Integrator A

Blue: Input voltage (Sw In A)

Is any other circuitry necessary in order to get the output as expected?

Thank you for your help in advance.