Other Parts Discussed in Thread: TINA-TI, , OPA725, OPA2743

Hey everyone!

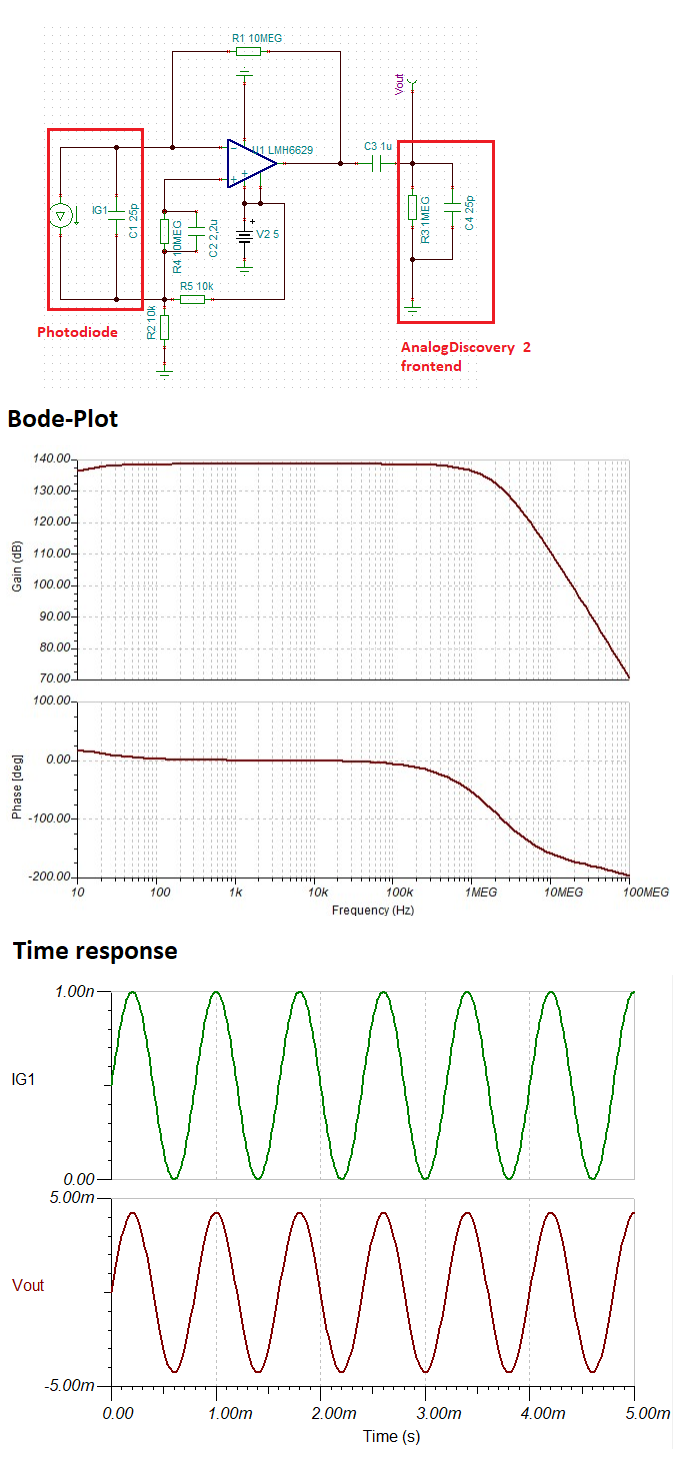

I need to build a first stage amplifier, a transimpedance amplifier, for a photodiode. The diode has a very small suface area, hence I expect a relatively low parallel capacitance but also (due to the application) a very low photocurrent, probably well below 5 nA. The photodiode will be part of a lock-in aplifier based absorption detection system, the modulation frequency of the excitation source (a LED) will be 1.25 kHz. I am looking for a maximum of gain in this first stage, so large feedback resistor values.

I used TINA-TI to simulate the circuit and I have to admit that I am not really sure what is going on. I tried to use large feedback resistors with 1 MOhm and 10 MOhm resistance. I found that to get a reasonable gain response I need to keep R4, the resistor at the noninverting input, close to the size of the feedback resistor.

1) My questions here: is that because of the input bias current?

2) I understand that the output voltage swing is within ~800 mV of the supply-rails, so I have to shift the level of the noninverting input into this range. Is it better to connect the anode of the photodiode to the same level (here 2.5V through voltage divider formed by R2 & R5) instead to ground as done in the schematics? In the simulation this seams to make no difference...

3) The GBWP of the LMH6629 makes me wonder why the AC simulation suggests a gain close to the expected gain up to frequencies well beyon 10 kHz. Is that realistic? I already doubt the results for 1.25 kHz with 10 MOhm feedback.

I have seen weird effects with a bunch of differen diode/opamp setups until now, so I try to understand all of this a little better instead of just fooling around. Any help or hint is appreciated.

Have a good time and thanks!

Ben