Other Parts Discussed in Thread: TLV3402

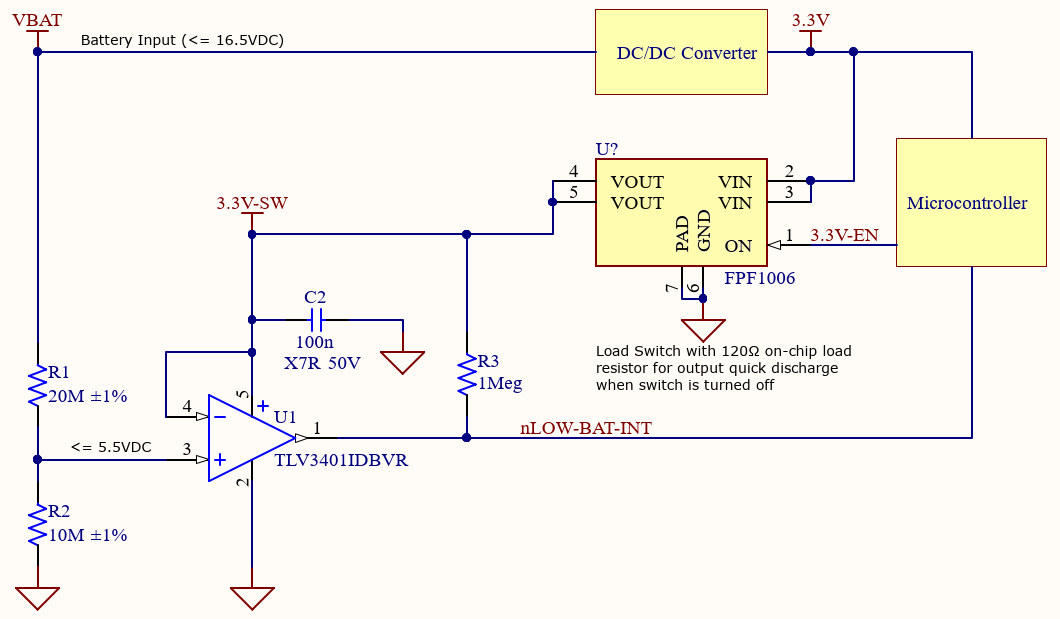

I have a question about exceeding, in a particular way, the absolute maximum rating of the input of the TLV3401. Below is a simplified schematic diagram of a circuit that we made a while back. The TLV3401 is used a detect a low battery voltage based upon a voltage divider of VBAT (1/3 divider). The battery voltage is converted to 3.3V, which powers a microcontroller and a load switch. The microcontroller can enable/disable the switched 3.3V, which powers the comparator (and other circuitry). The load switch has an internal 120ohm discharge resistor, which is present when the switch is turned off.

We have a recent situation where we have a somewhat larger battery voltage than originally assumed. The battery voltage could reach 16.5VDC, and in turn the voltage divider output could reach 5.5VDC. In the event that the switch is powered off (e.g. when the battery is first connected or by control of the uC), VCC of the TLV3401 would be 0VDC, while 5.5V is applied to the “+” input via a 20MegOhm resistor. That voltage exceeds the absolute maximum rating of “VCC + 5”.

Can you tell me more about the internal structure of the TLV3401 and the effect of applying a current-limited 5.5V to the input pin while VCC = 0? Is there a risk of damage, reduced reliability, etc.? I think normally in this situation the ESD diodes would conduct and because the current is limited, it might be ok. However I see this e2e post for the TLV3402 https://e2e.ti.com/support/amplifiers/f/14/t/209321, where it says the input ESD cells are designed to stay off.