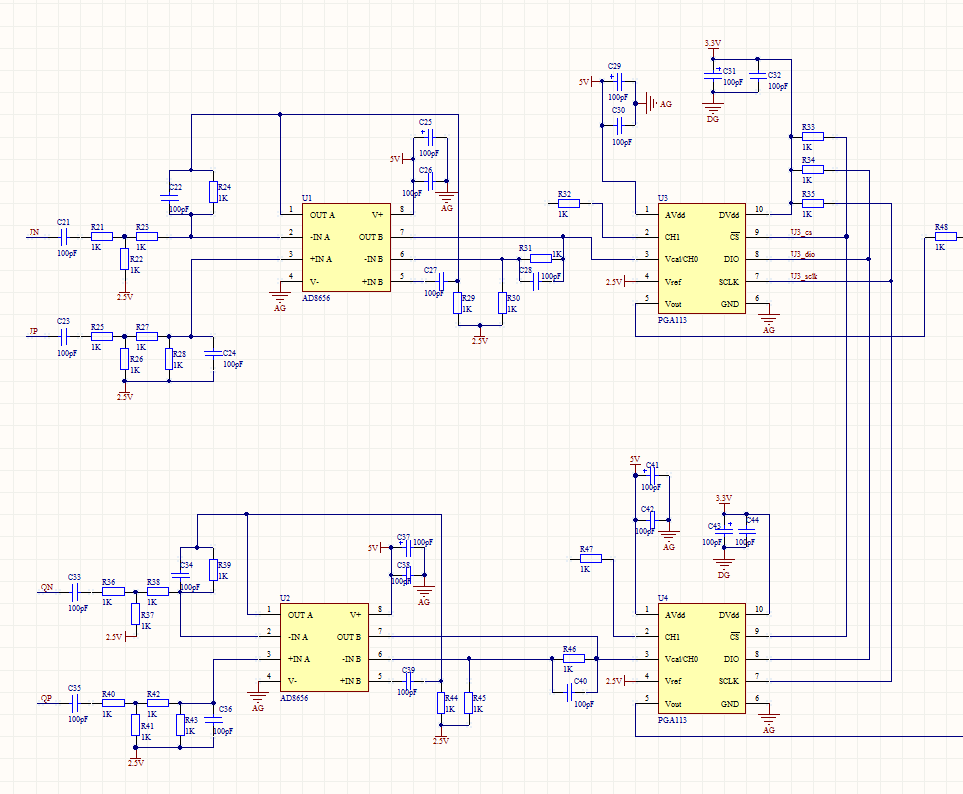

#define PGA_SET_SCL() GPIO_SetBits(GPIOI, GPIO_Pin_2) // PI2-> U3_sclk

#define PGA_CLR_SCL() GPIO_ResetBits(GPIOI, GPIO_Pin_2)

#define PGA_SET_CS() GPIO_SetBits(GPIOI, GPIO_Pin_0) // PI0-> U3_cs

#define PGA_CLR_CS() GPIO_ResetBits(GPIOI, GPIO_Pin_0)

#define PGA_SET_DIO() GPIO_SetBits(GPIOI, GPIO_Pin_1) // PI1-> U3_dio

#define PGA_CLR_DIO() GPIO_ResetBits(GPIOI, GPIO_Pin_1)

void PGA113_Write(u16 ads_dat) //MODE 1.1

{

unsigned char i;

PGA_SET_CS();

PGA_SET_SCL();

PGA_CLR_CS();

DELAY(0x100);

PGA_CLR_SCL();

DELAY(0x100);

for(i = 0; i < 16;i++)

{

PGA_SET_SCL();

if(ads_dat&0x8000)

PGA_SET_DIO();

else

PGA_CLR_DIO();

DELAY(0x100);

PGA_CLR_SCL();

ads_dat <<= 1;

DELAY(0x100);

}

PGA_SET_SCL();

DELAY(0x100);

PGA_SET_CS();

}

int main(void)

{

PGA113_Initiate();

while(1)

{

PGA113_Write(0x2A40); //0x0010 1010 0100 0000

}

}

Yellow is SCLK, blue is DIO.The output waveform cannot be amplified,why?