Other Parts Discussed in Thread: TLE2071, TLE2072, CD4051B, CD74HC4051

Dear Forum,

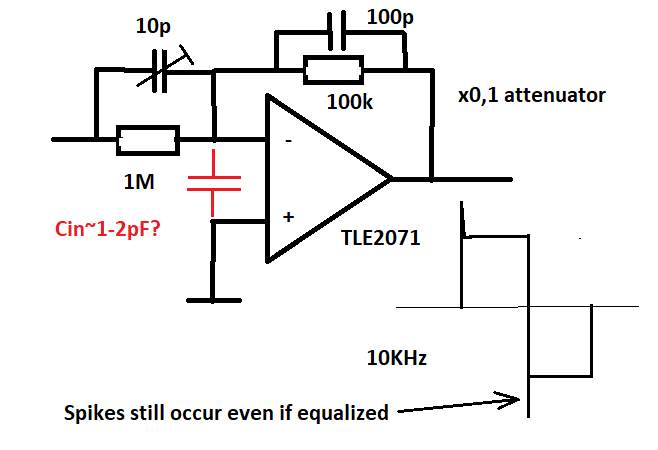

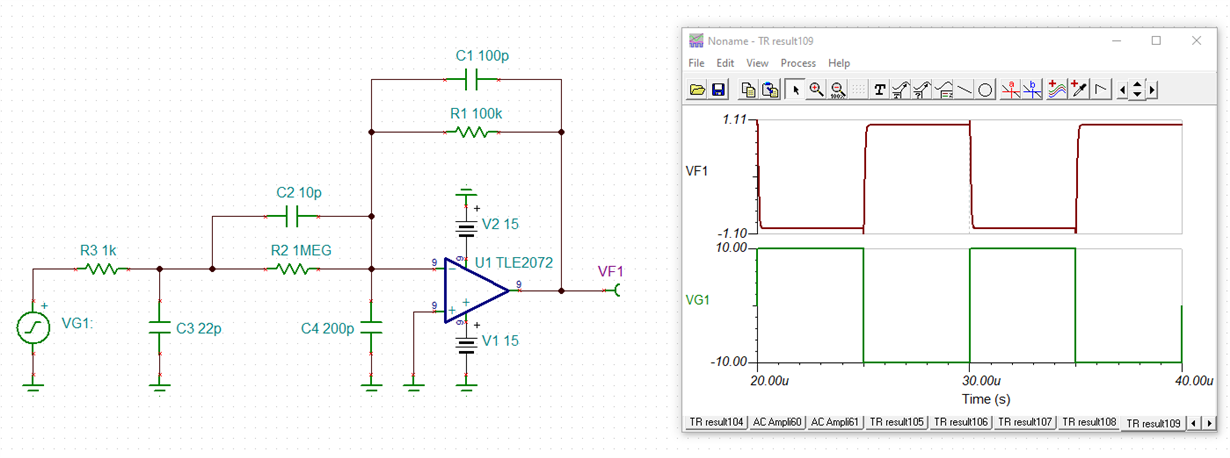

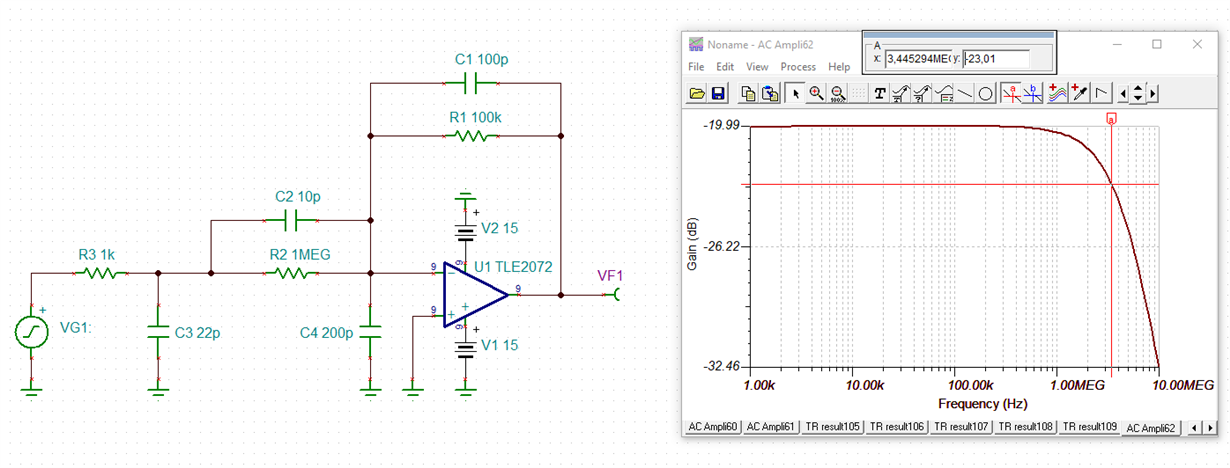

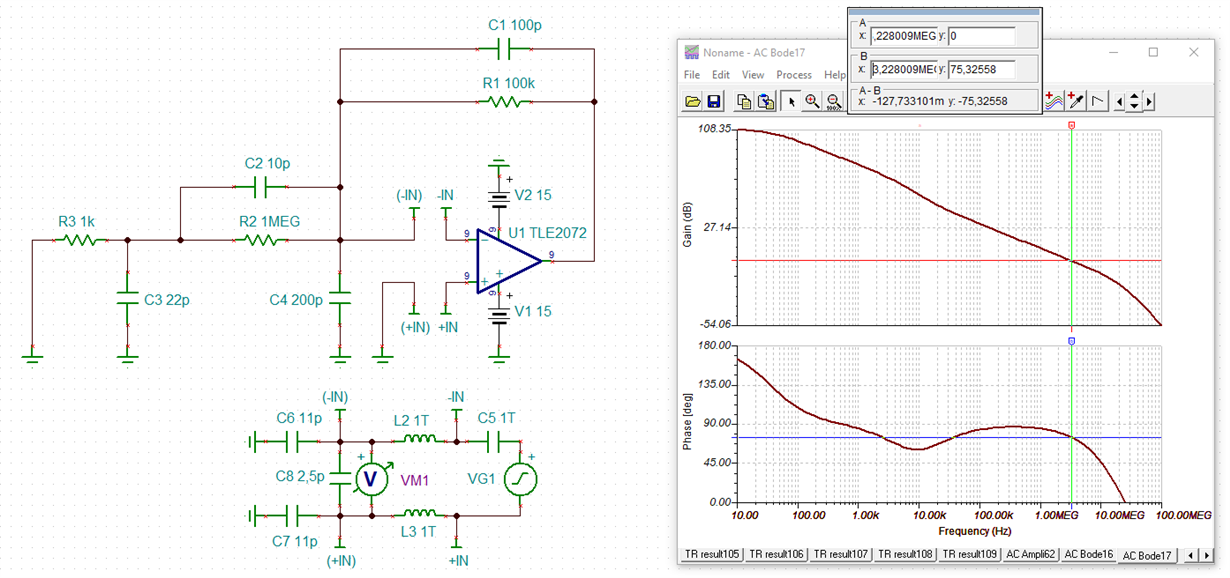

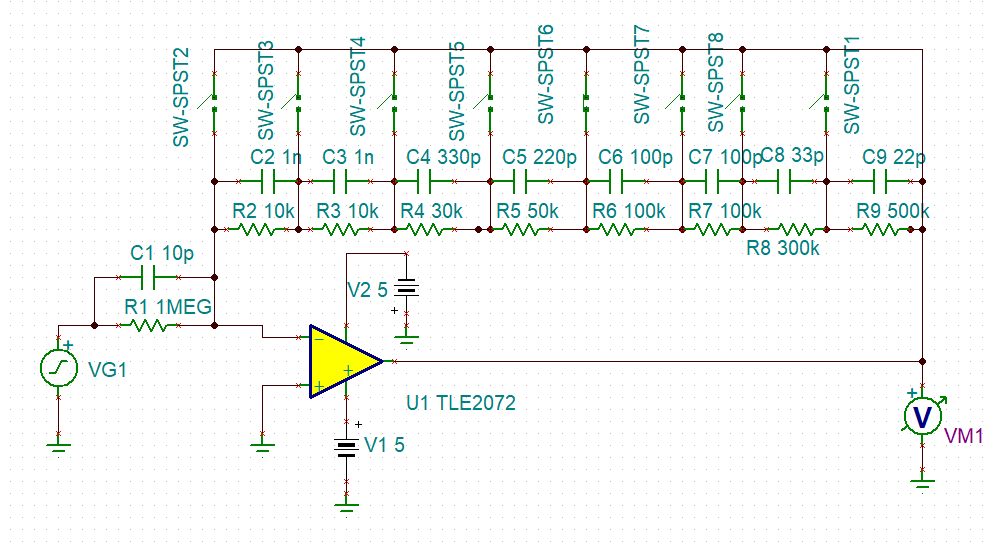

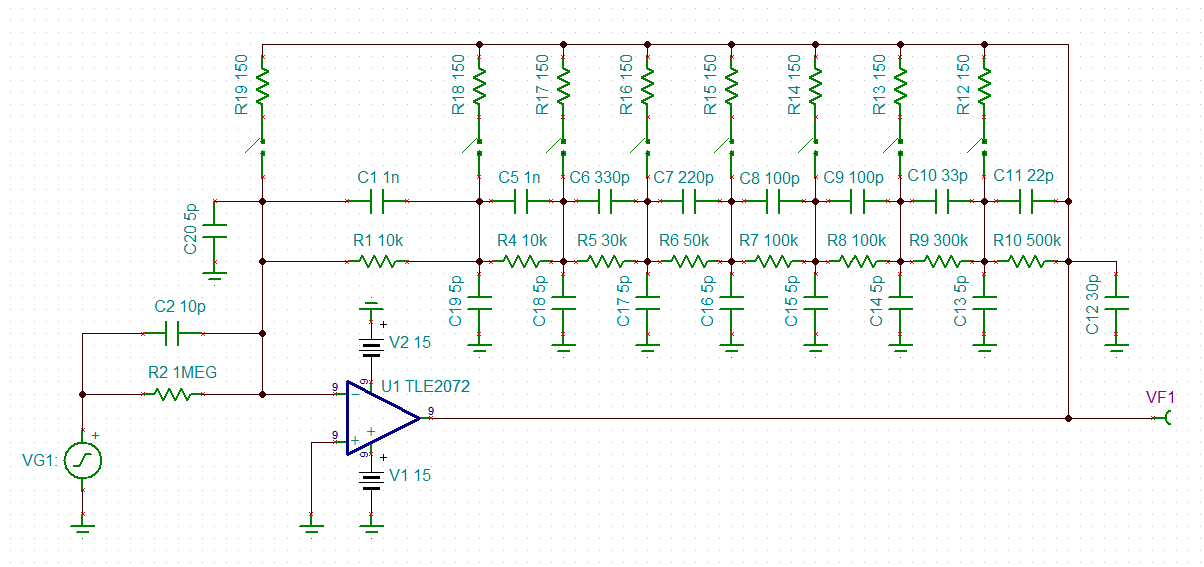

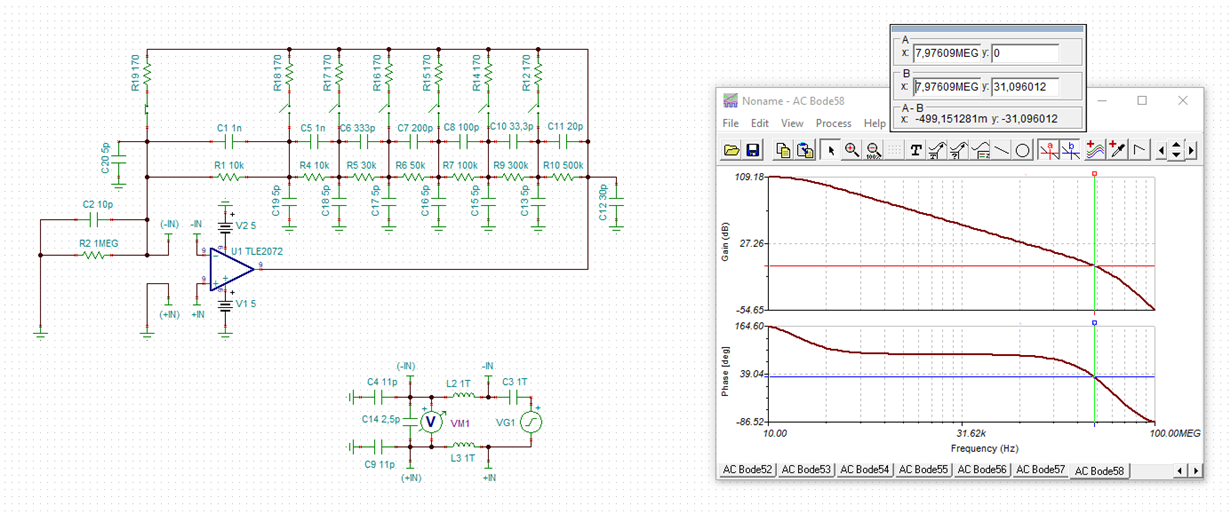

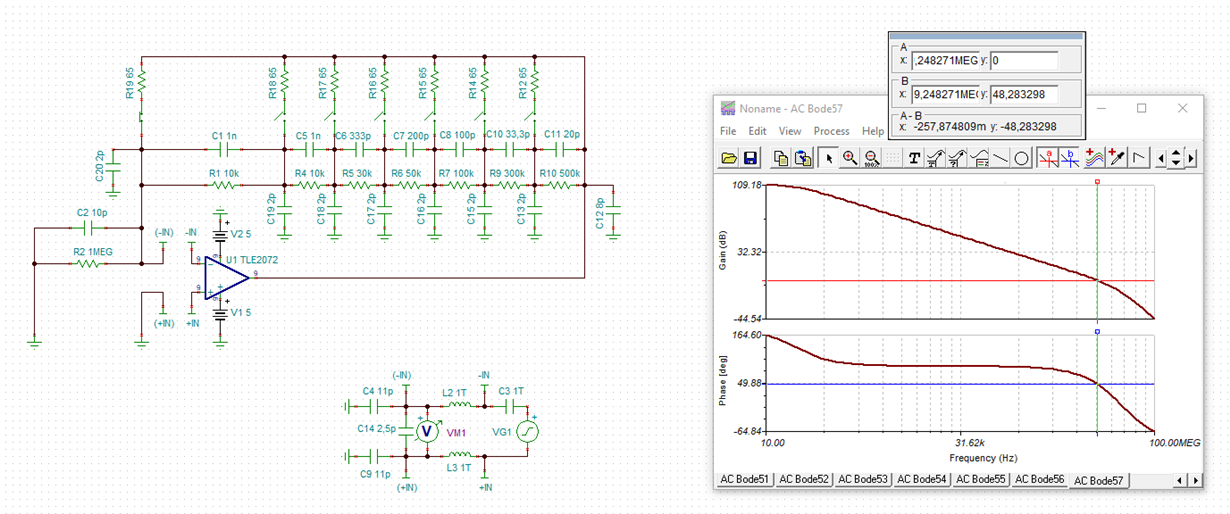

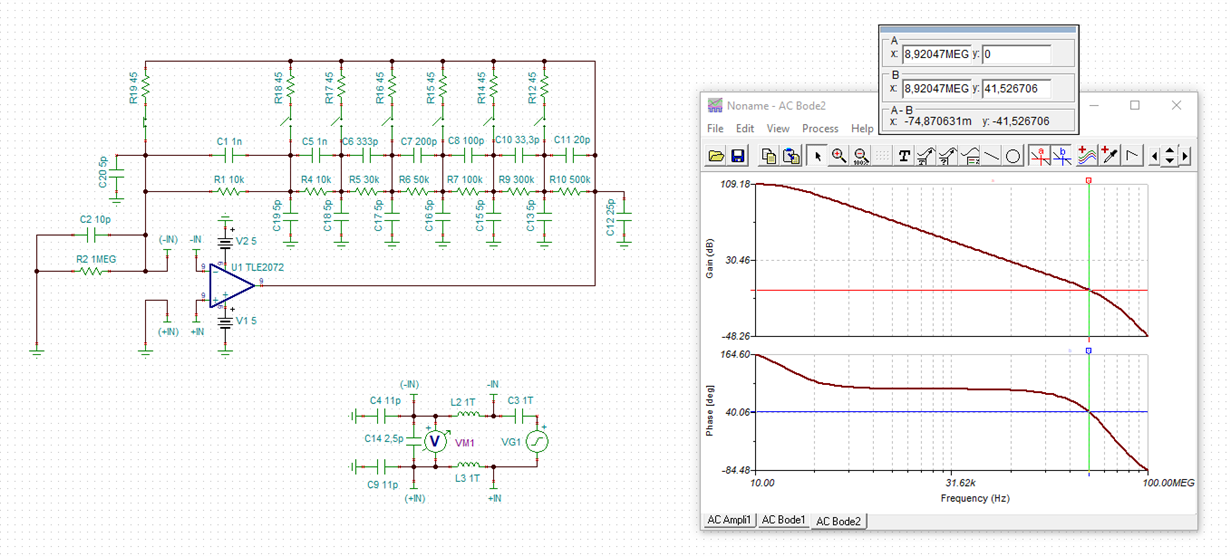

I have bulilt an active attenuator using TLE2072A. This type was choosen thanks for its expectional slew-rate value (>30uV/s) ensuring good signal shape fidelity. Additionally, the circuit has a high input impedance,

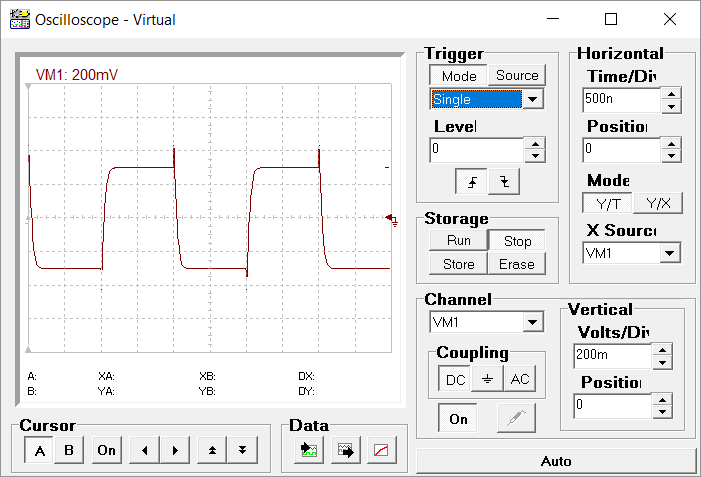

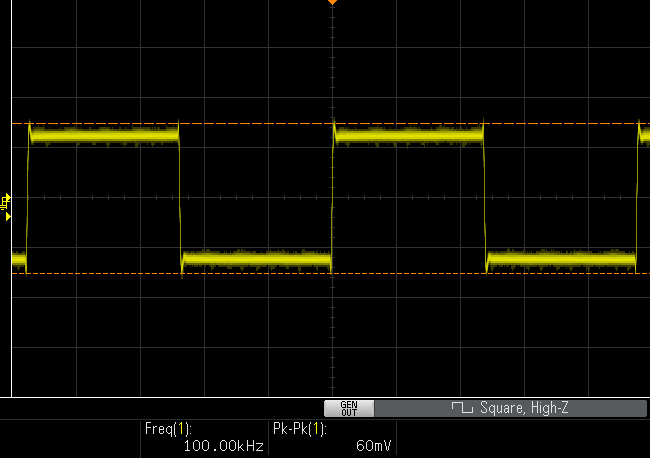

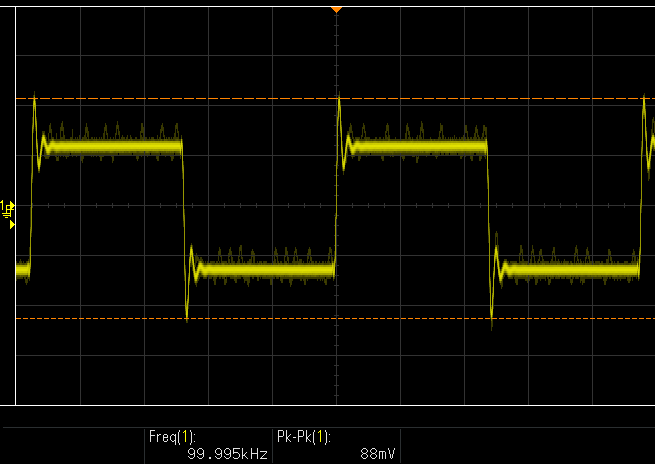

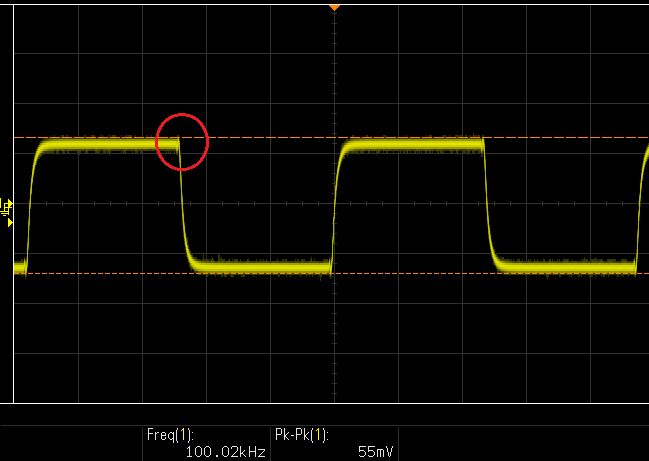

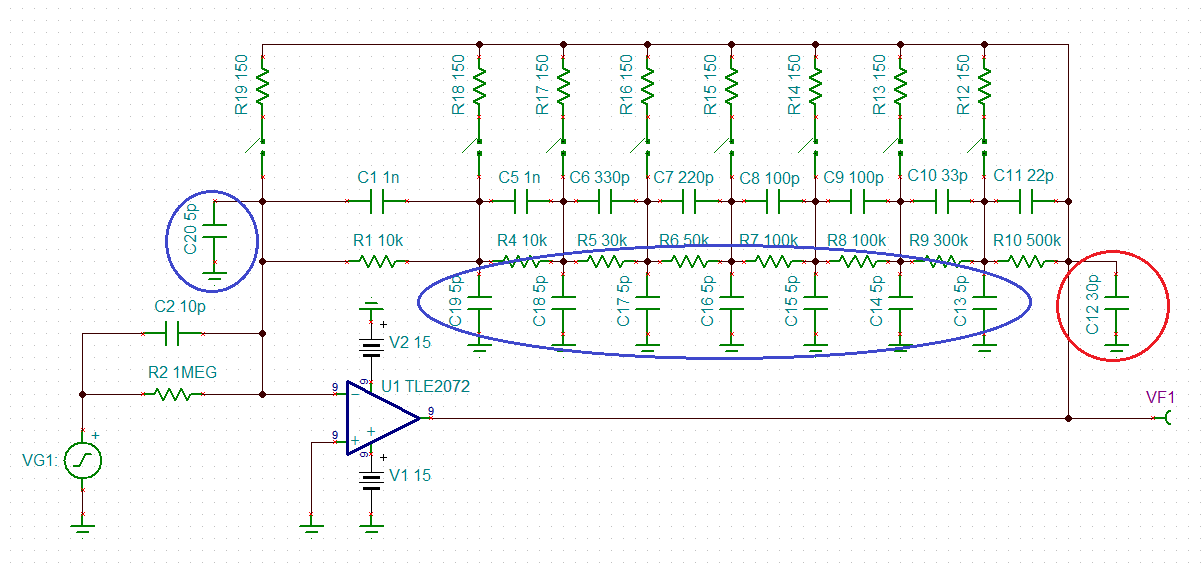

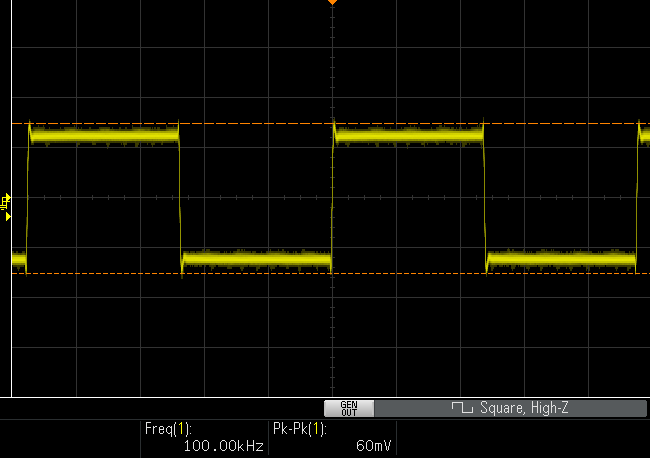

thus input/parasitic capacitances had to be compensated. Unfortunately, after compenstaing, large spikes still occur at signal transistions (square wave transition edges). Spikes cannot be trimed out.

I do not understand why the spikes, maybe due to less phase margin (stability issues) and the large capacitances. However, the external compensation shall improve the over stabulity.

Joseph