Other Parts Discussed in Thread: OPA847

Hi,

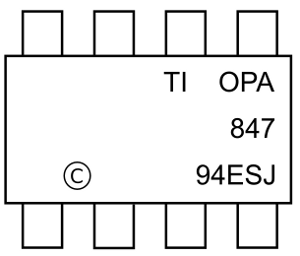

I apologize ahead of time for hijacking this forum for what would seem to be a simple question. I recently attempted to use an OPA847 in a standard non-inverting configuration as discussed in the spec sheet (Fig. 1) . I used 20V/V with Rf and Rg as recommended. However, as I turned the Amp on, I noticed a large DC offset, -4V when 1Mohm coupled to a scope. I am aware that input voltage offset (+/- 0.6mV at worst) and input offset current (+/- 0.85uA at worst) could come to play but -4V seems excessive. As a test, I disconnected everything leaving only Vcc. Strangely, I saw the same DC offset. Since I have a few OPA847s, I swapped to another chip. Again, the same offset. When I measure the voltage on the input pins when they are not connected to anything they read -4.3V - on each. I have the 6.8uF and 0.1uF caps to decouple the supplies as recommended (the 0.1uF is on the supply pins). The chip is on a 4-layer board with middle ground planes. Holes in the ground plane were placed around the input/output pins as recommended. Since it seems so bizzare, I looked at the top markings on the chip. I tried to compare with the published TI markings found here but didn't find the markings that I see on the chips. Below is a sketch of what I have:

The closest marking I found on the link above is the fifth down, yet it is not exactly as shown in my sketch. The copy-right mark is between what I thought to be pins 1&2 and not exactly above pin 1 as one would expect. Also, the (C) mark of itself is somewhat strange since it is not a full white dot nor an embedded mark into the chip (circular dip). Calls to tech support didn't help much and they agreed that I should assume the (C) is between pins 1 and 2. Since I get such odd behavior in DC offset, I just wanted to ask whether anyone have seen such a thing and maybe I have the pins messed-up?

If anyone has any hints I would greatly appreciate it,

Thanks,

Gideon