Part Number: OPA189

Other Parts Discussed in Thread: TINA-TI, INA149, LMP8480, OPA388

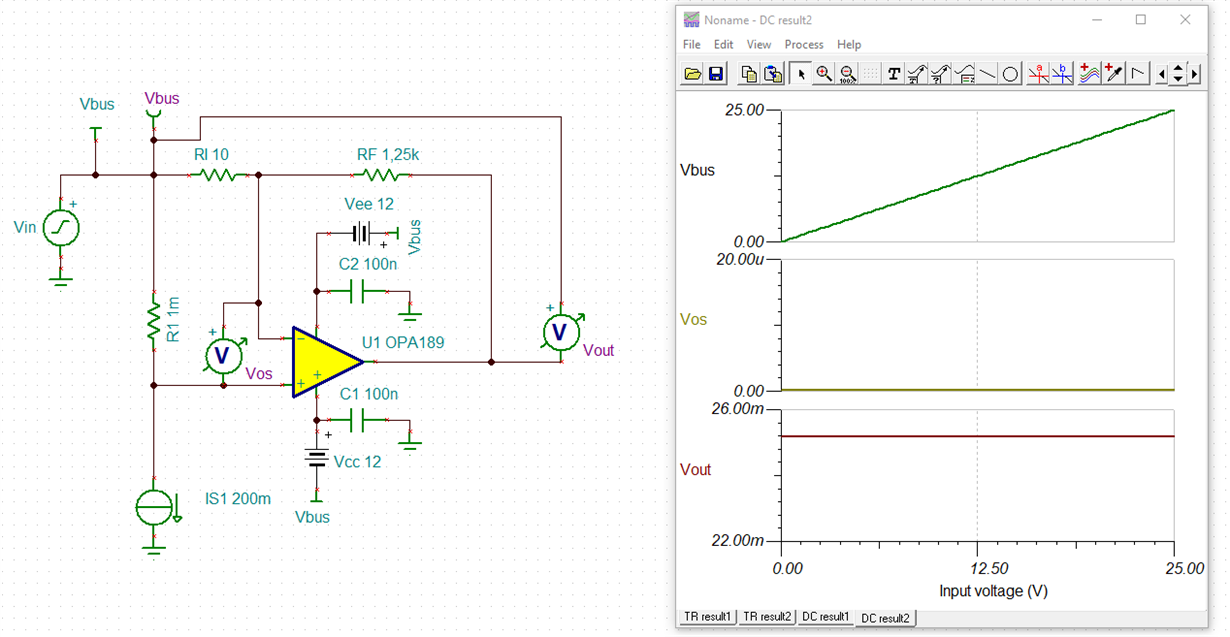

I am working on a design for a high-side current monitoring circuit, using an OPA189. A very simplified schematic is shown below. I have simulated this simplified schematic to confirm it generates the behaviors I am about to describe.

The OpAmp receives floating +/- 12V power, and the entire circuit sits at voltage Vbus.

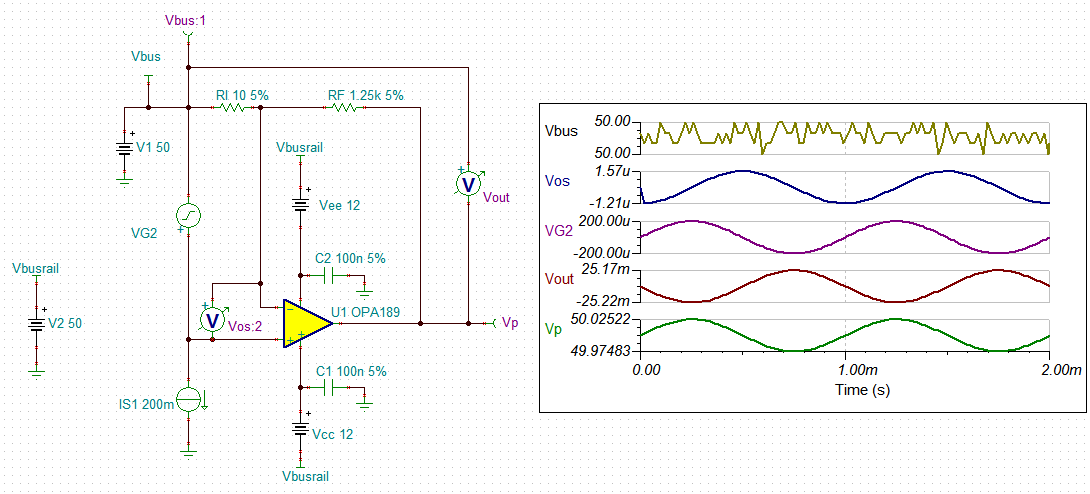

When Vbus = 0V, the circuit performs as expected. As Vbus increases from 0V to 24V, performance worsens. The signal at OUT increases from less than 0.1% error, to over 5% error (closed loop gain = 125). When Vbus = 50V, the simulator I am using refuses to complete the simulation.

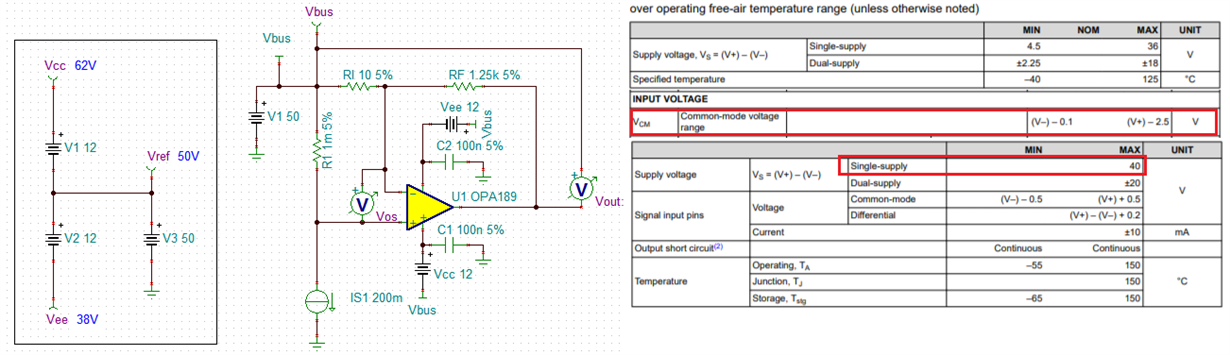

My observation is that Vofs reported by SPICE (I probe the delta between (+) and (-) input pins) grows larger and larger, well beyond the datasheet limits, as Vbus increases. Note there is no explicit connection between the OpAmp and GND. VCC and VEE appear to be +/- 12V relative to the common-mode input signals. In this simulation, the voltage across Rsense is a few millivolts. Therefore the common-mode input that the OpAmp sees is for all practical purposes perfectly centered between VCC and VEE.

My assumption is that the op-amp SPICE model has internal references to the global GROUND node [notionally V(n000)], and does not perform as expected when floated to some arbitrary voltage away from ground. Can someone confirm this to be the case?

Thanks,

Will

EDIT: Changed "Vsense" to say "Rsense"