Other Parts Discussed in Thread: OPA810, OPA857, LMH32401

Hi sir,

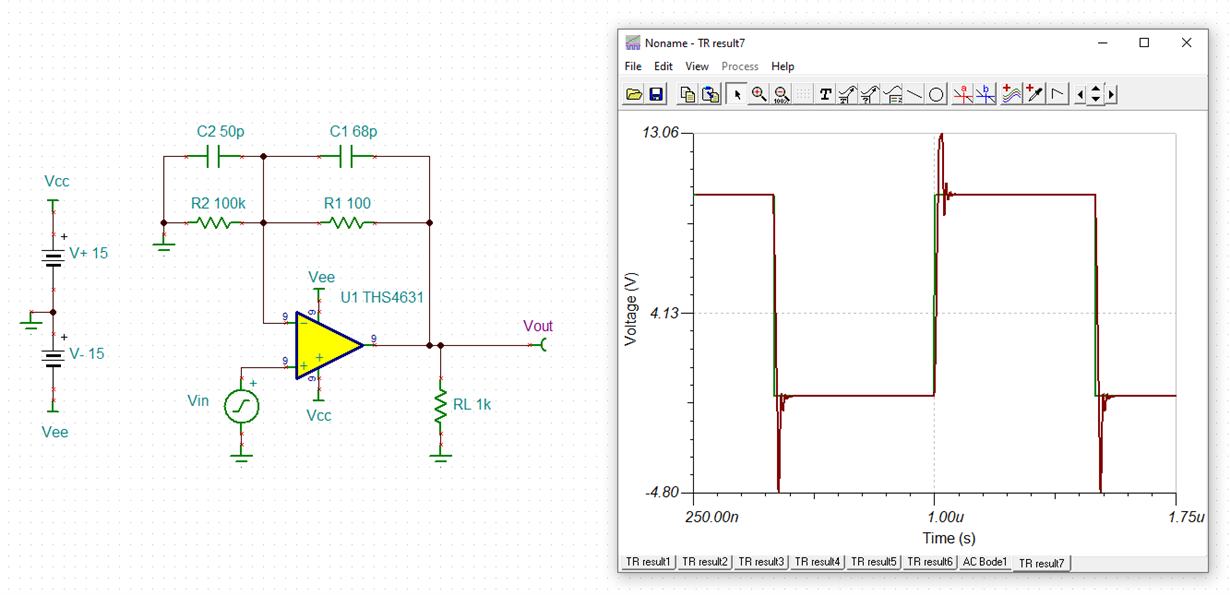

I have a technical problem on ths4631.

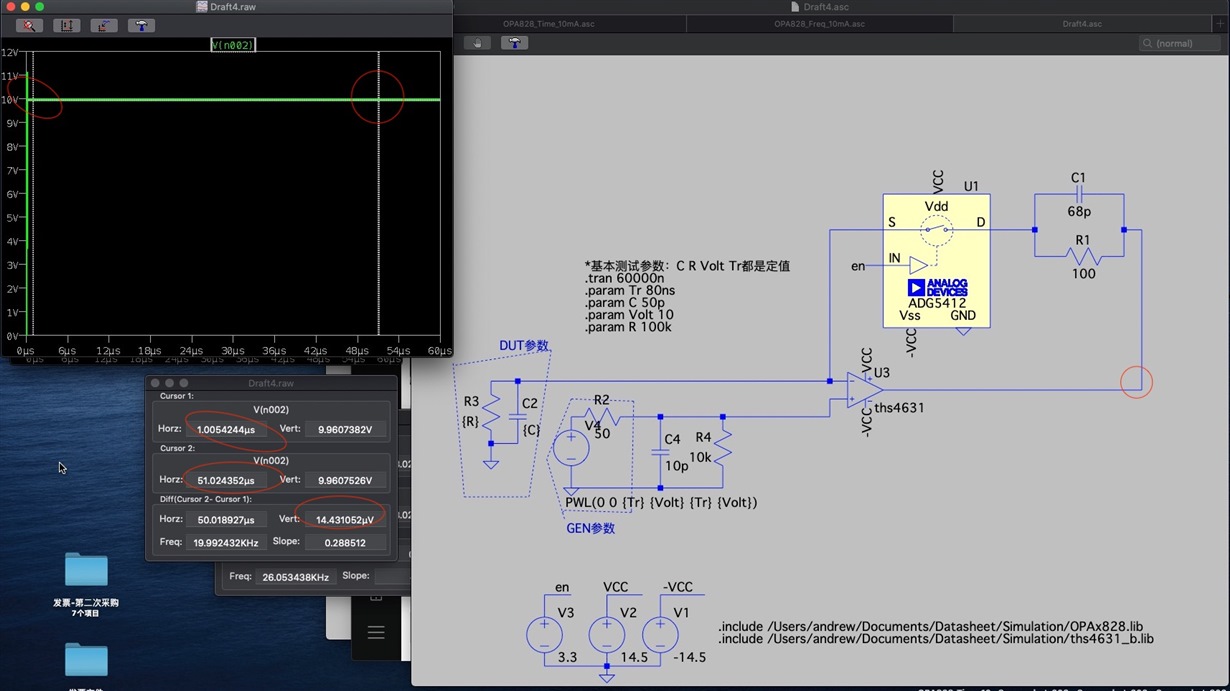

when testing the output port,

the difference between the test value of 1us and that of 51us is 14uv.

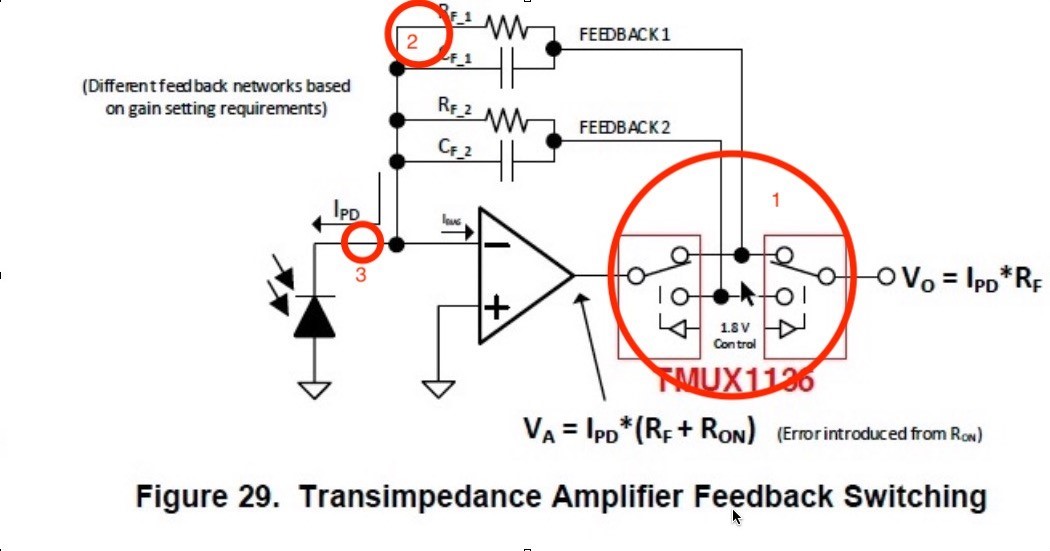

How to modify the circuit so that the output can be stabilized to 0.6% DD of the stable output within 500ns.

Thank you for your suggestion.