Other Parts Discussed in Thread: ALLIGATOR

Hi,

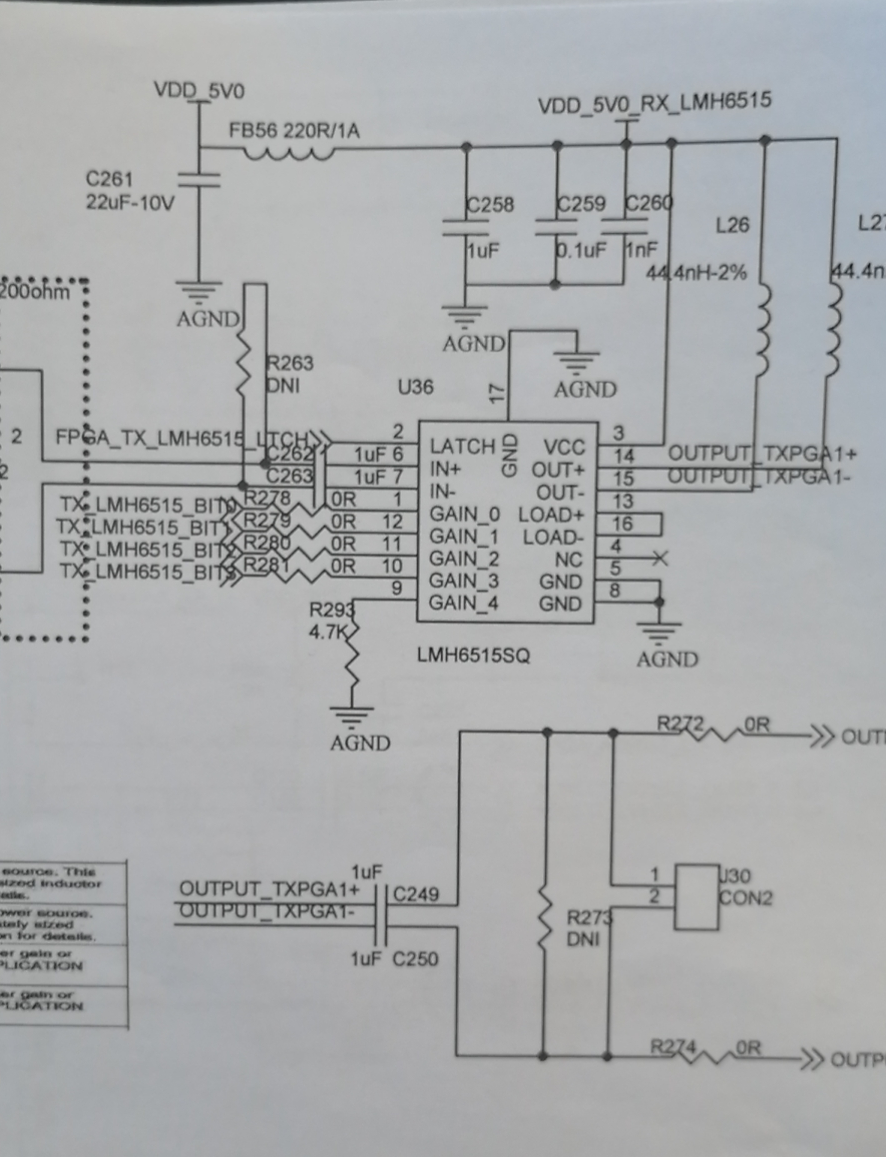

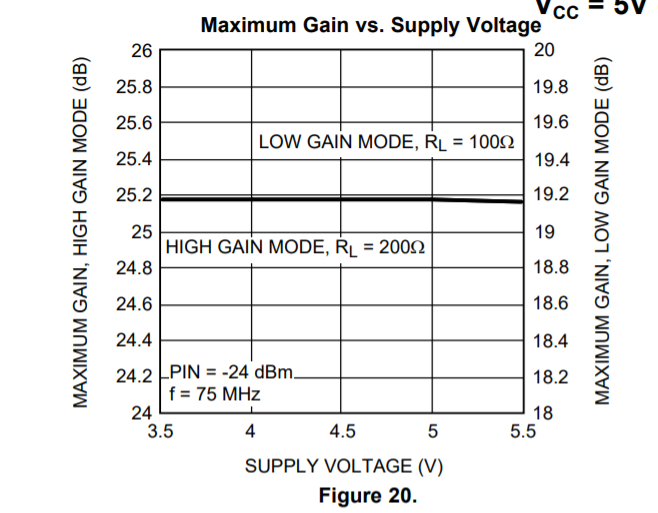

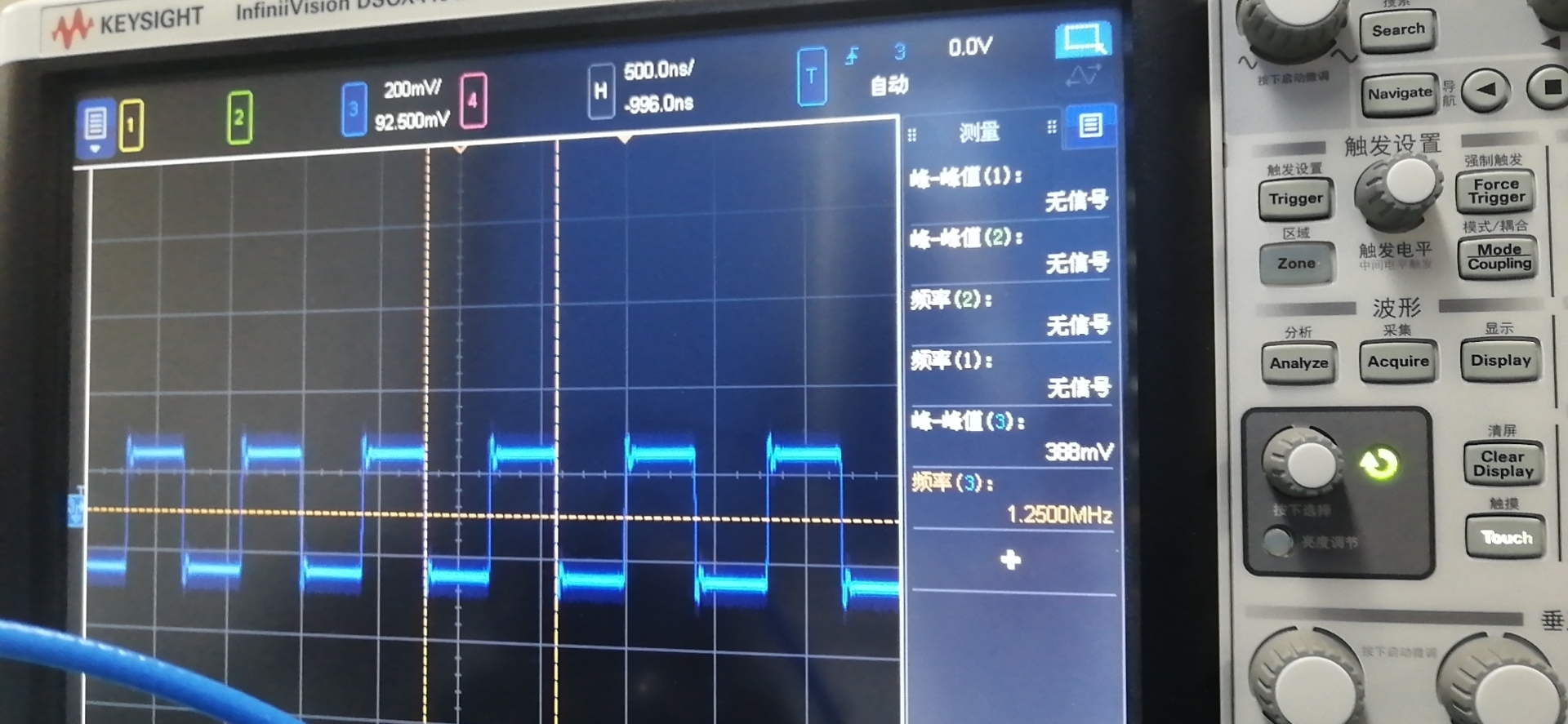

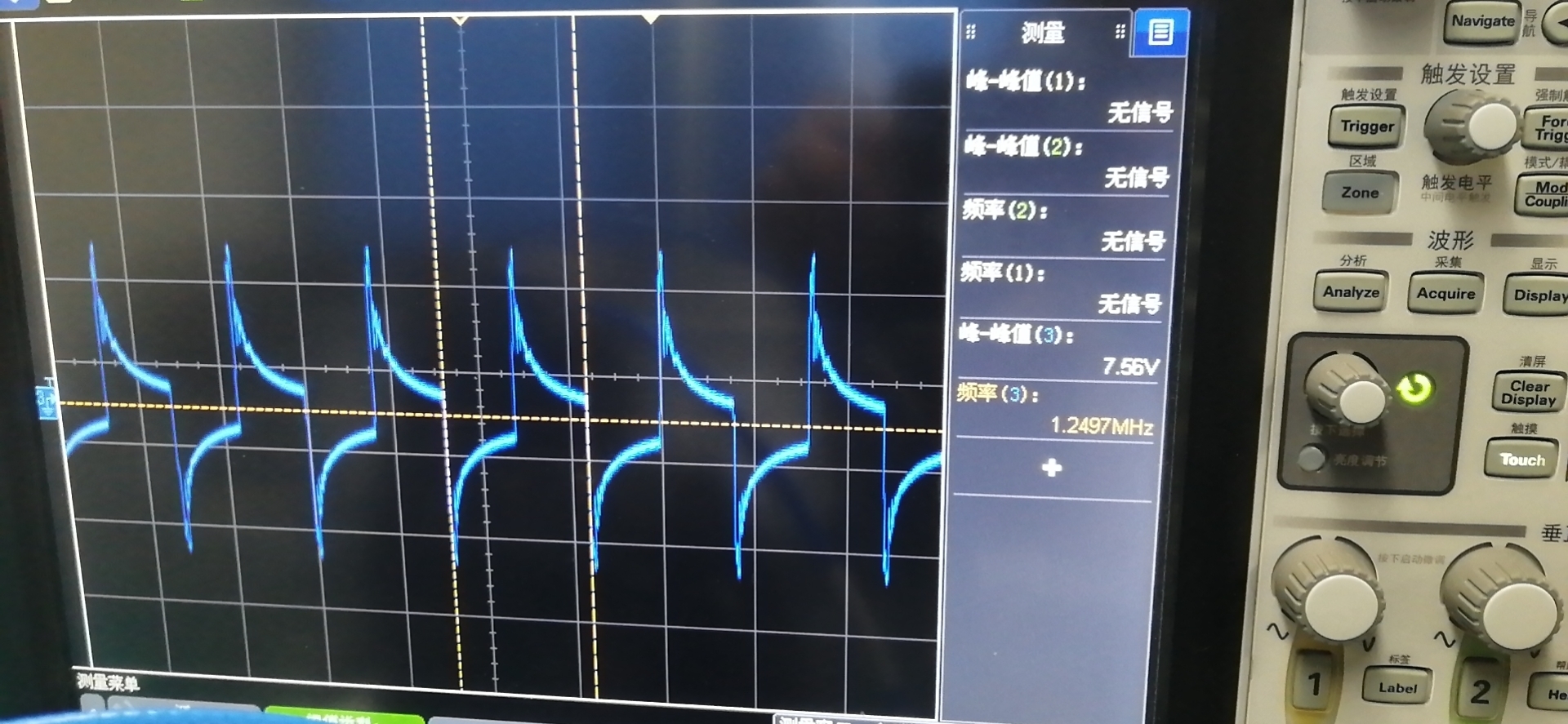

Please find the schematic for LMH6515 in the below. The input signal is 500mVpp at 25Mhz, but the output level is just 80mVpp. Could you please help review the schematic and give your suggestions? Thanks.