Other Parts Discussed in Thread: TINA-TI

Hi team,

1. Customer feedback is as follows:

The customer produced a batch of products (317pcs) and reported a total of 5 sets of equipment with performance failure. One of them reported a performance failure when it was powered on at room temperature, and the other 4 reported a performance failure when it was taken out of the high temperature box after it was aged at 50 ℃ for 2 hours.

According to the disassembly analysis, TLV2172 failed. After TLV2172 was replaced, the failure was removed and the function returned to normal.

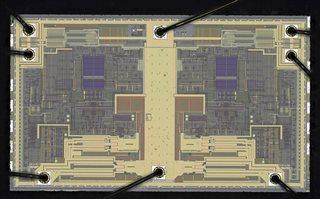

2、The customer entrusts the testing organization to analyze the fault TLV2172 . Through the analysis of ultrasonic and X-ray, the following phenomena are found in the faulty 3pcs

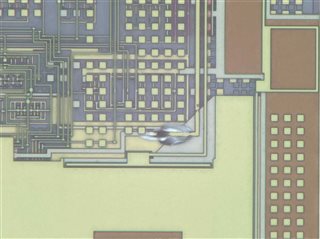

(1) There is an unknown mark in the inner layer

(2) Bottom X-ray found layered

1 is normal, 2, 3 is bad

(3)Corrosion and burning marks are found on the tendon after opening

(4)All the opening products are from the same batch

The customer purchased TLV2172IDGKR through 云汉芯城, and the order number of 云汉芯城 purchased from TI: T01057115, T01033854.

Please help to analyze the causes of the above results