Hello dear Ti community.

I know decoupling thread was explained thousand times and there is some general rules that should be followed.

But I've got some other questions that might be important as well.

So, I will try to explain my design and why I really care about those.

My desing is builded around few opamps and analog muxes.

I will look like this :

1x OPA1604 (audio input stage) 3x paralleled OPA1622 which will drive load directly (headphones), and analog mux around OPA1604 for gain manipulation (powered from bipolar supply).

This is one channel only.

I've got rather good PSU builded around ultra low noise LDO's.

Most common technique is to place 100nF capacitor as close as possible to IC pins (with opamps that are hi current output it's often recommended to place a bulk capacitor to provide enough charge).

And I already made that, each opamp got it's own bulk capacitor (10uF) followed by 100nF capacitor + another smaller like 1000pF.

My PCB is 4 layer board, so I can use internal layer for power to avoid thin/long power trace with significant inductance, or I can use outer layer to route fat enough power traces.

So PCb could be handled well by me and it shouldn't be an issue here.

Question is:

- should I isolate each opamp power supply from each other via ferrite bread (even if they are tends to work at higher freq) or resistor (I will affect dynamic range).

- or I should forget about it?

Should I include that kind of isolation? Imporant question is where should I care about it and when it's not required.

From theoretical point of view it's look promising, because it will improve opamp PSRR and it will make also make power supply cleaner, because there will be no "coupling contamination" that could harm other opamps.

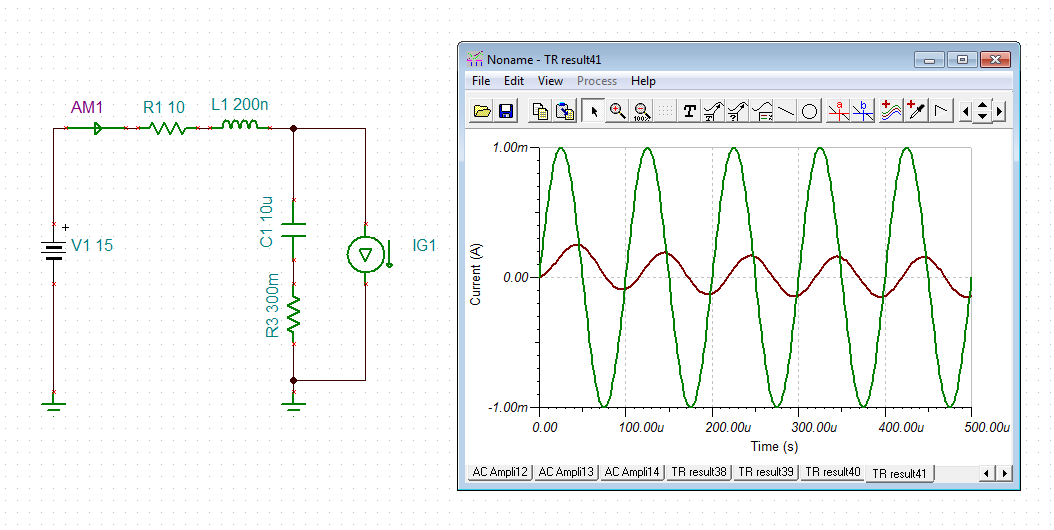

I thinkg this is important because my output stage is AB class amplifier, that draw only half rectified current.

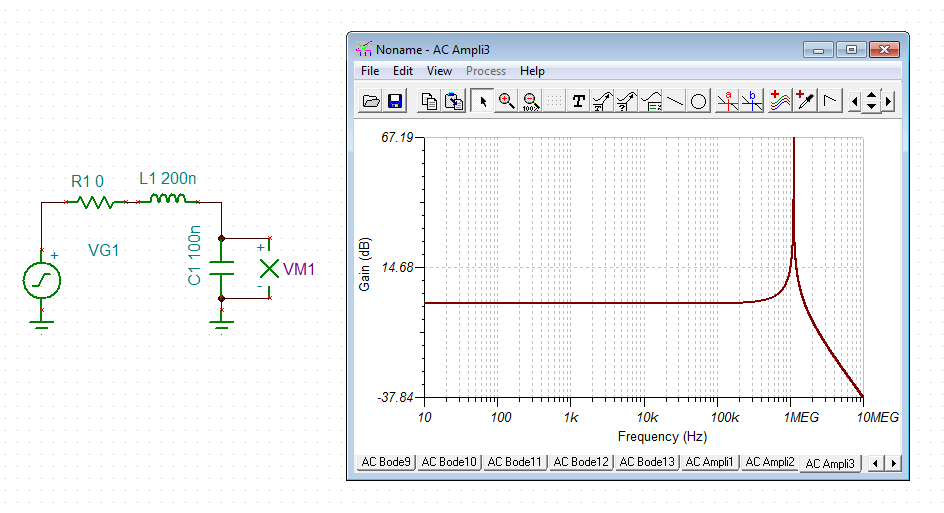

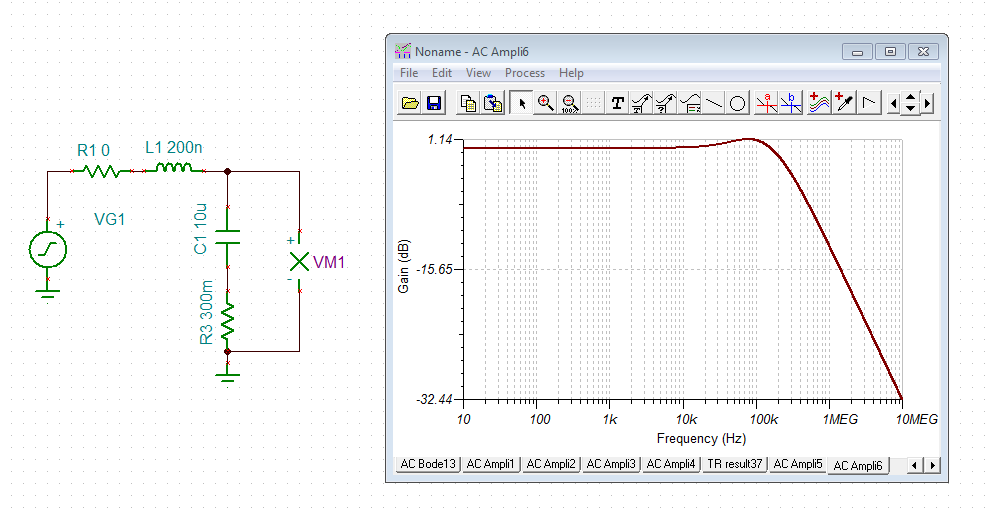

I also heard that placing multiple small value capacitors (like 100nF) for each power supply IC pins could resonate if connected to same power plane.

To avoid this I will need to add some damping.

So I'm looking for some more extended explaination of my post, because I'm aware about some things but I assume that it's still not enough.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.