Other Parts Discussed in Thread: LAUNCHXL-F28379D, C2000WARE,

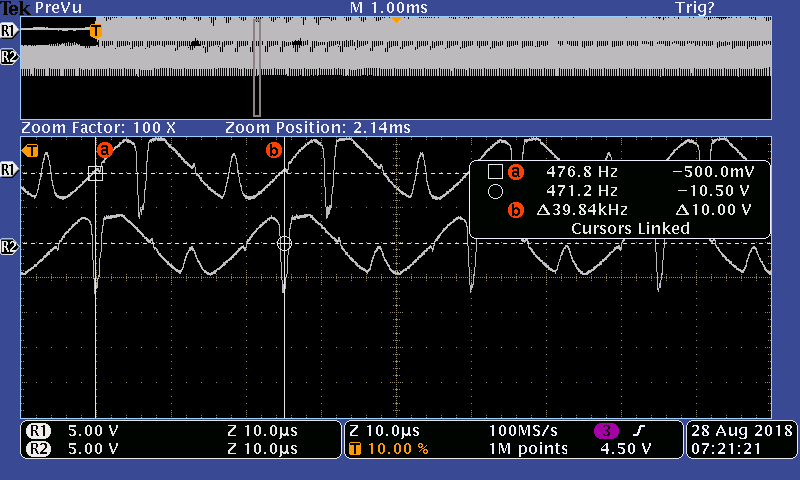

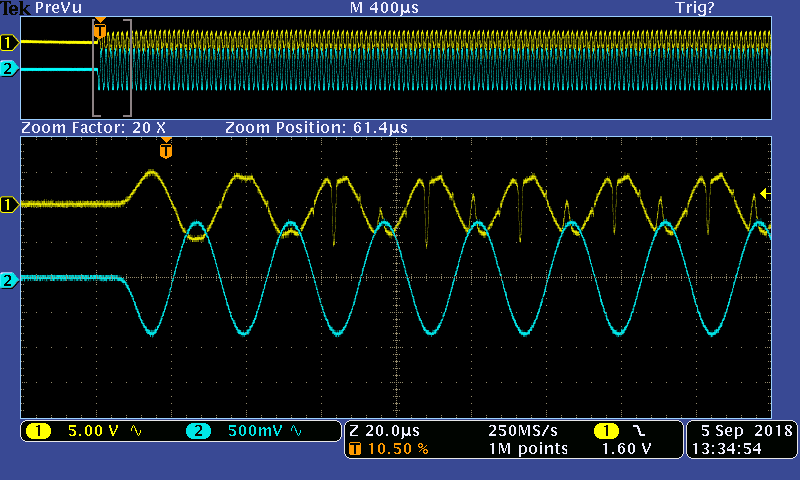

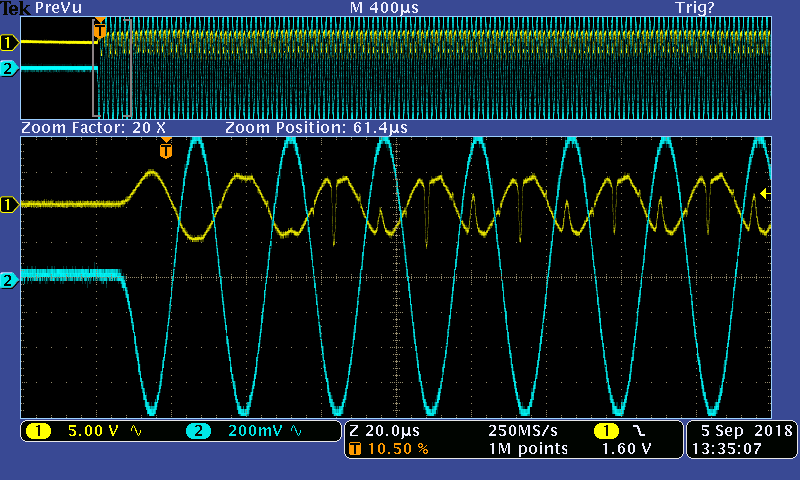

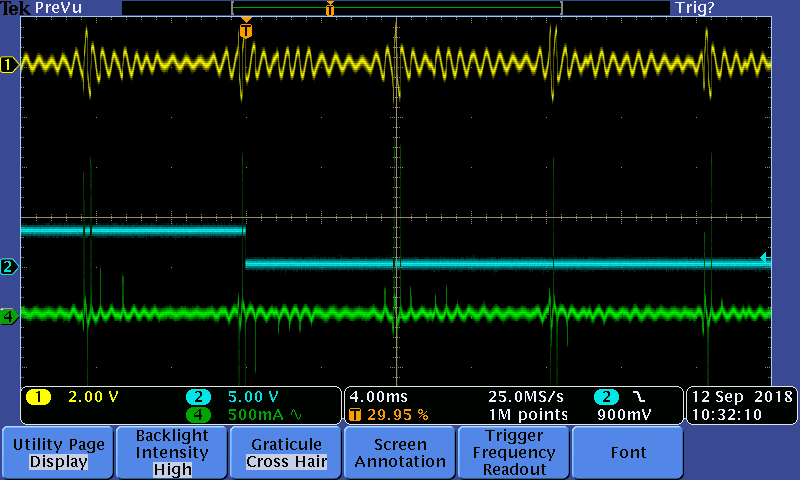

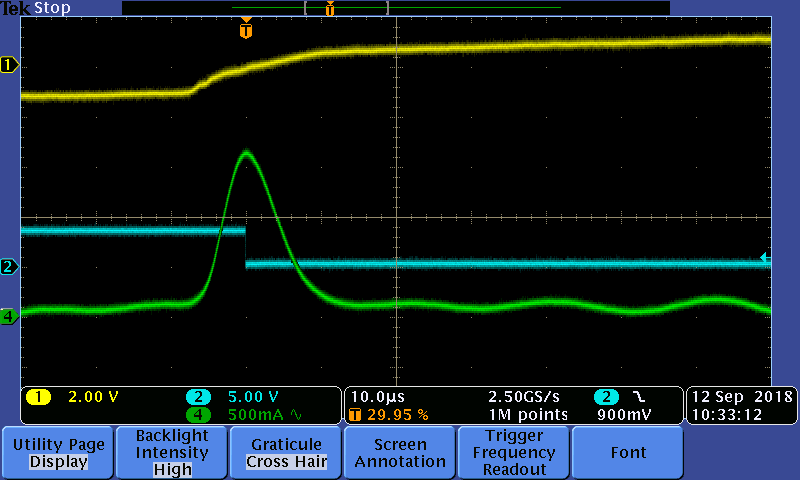

We're unable to get an OFDM PLC application to communicate successfully. Our 64 carriers are in the 25k to 65kHz i.e. CENELEC A band. Investigating I used a function generator to generate discrete sine waves in lieu of the OFDM signal. I connected the output of the function generator to the AFE031 'TX_PGA_IN' pin. Function generator output was 3.1Vpp 1.65Vos. AFE031 'TXPGA' gain was set to 0.5. Building 120VAC was connected to secondary of coupling transformer after series LC. Output was monitored AFE031 'PA_OUT'. I expected in band sine waves, amplified by 3.25, to be seen at the output. This was the case for ~25k-30kHz. However at 35k to 40kHz the output was severely distorted. I've attached a screen shot of the distorted waveform and AFE031 schematic. Does the distortion make sense? Does the design make sense?

thanks

Mark