Hi Team

to calculate Min Duty and Max Duty, I need the below information.

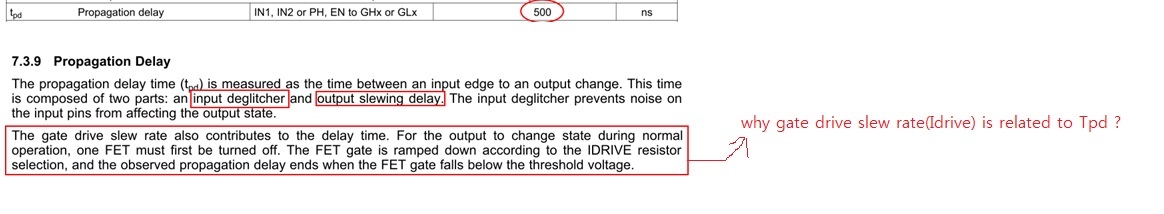

D/S say Tpd = TYP 0.5usec.

D/S say Tpd is composed of the input deglitcher and the output slewing delay.

I understand why the input deglitcher belongs to Tpd.

[1] However, I cannot understand why the gate drive slew rate by IDRIVE is related to Tpd.

Can you explain it to me ?

[2] Also the spec of Tpd = TYP 0.5usec includes both “the input deglitcher” and “the output slewing delay” ?

If that, do you know what is the IDRIVE setting and the Load capacitance for the spec of Tpd = TYP 0.5usec ?

Or,,, the spec of Tpd = TYP 0.5usec is only including the input deglitcher ?

[3] what is the delay time for the input deglitcher among Tpd = TYP 0.5usec ?