Hi,

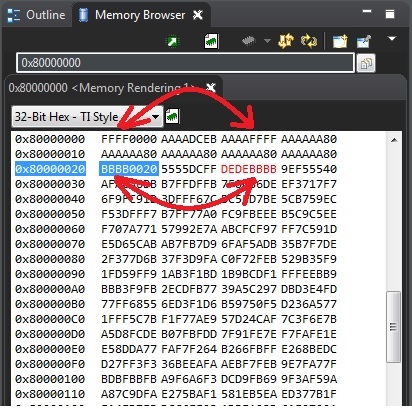

We use AM4377 processor in our custom project board and we face the problem of unsuccesful DDR3 initialization when uploading the GEL files. We modified the IDKAM437X DDR3 settings in AM43xx_EMIFconfig_HWlvl as we based the hardware part on IDKAM437X. The DDR3 used in different so there are a lot of changes to be done. Unfortunatelly, DDR3 reading test is not passed. We wrote our code for broader analysis and discovered that there is a pattern in those errors - every time we access the cell of the following address endings: 0x0 ; 0x1 ; 0x8 ; 0x9 we get the wrong value. For instance our test reults look like that:

CortexA9: GEL Output: Binary: Addr:0x80000000, Expected: 0xAAAAAAAA, Read: 0xAAAA0020

CortexA9: GEL Output: Binary: Addr:0x80000001, Expected: 0xAAAAAAAA, Read: 0xAAAADCEB

CortexA9: GEL Output: Binary: Addr:0x80000002, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x80000003, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x80000004, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x80000005, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x80000006, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x80000007, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x80000008, Expected: 0xAAAAAAAA, Read: 0xAAAA0000

CortexA9: GEL Output: Binary: Addr:0x80000009, Expected: 0xAAAAAAAA, Read: 0xAAAAFCFF

CortexA9: GEL Output: Binary: Addr:0x8000000A, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x8000000B, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x8000000C, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x8000000D, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

CortexA9: GEL Output: Binary: Addr:0x8000000E, Expected: 0xAAAAAAAA, Read: 0xAAAAAAAA

We have tried many different memory settings in the registers: CTRL_DDR_ADDRCTRL_IOCTRL, CTRL_DDR_ADDRCTRL_WDX_IOCTRL, CTRL_DDR_DATAX_IOCTRL, EMIF4D_DDR_PHY_CTRL_1, EMIF4D_SDRAM_CONFIG, EMIF4D_SDRAM_TIMING_X, EMIF4D_SDRAM_REFRESH_CTRL, EMIF4D_SDRAM_OUTPUT_IMPEDANCE_CALIBRATION_CONFIG according to the DDR memory datasheet.

We are out of ideas even after reading the TI tutorials about DDR configuration. Could you please advise us in which part of our configuration the error could be? - do we have to look deeply into DDR3 size (rows, columns, banks) or its timing? We are noobies in this subject so maybe there is someone more experienced in DDR3 programming who would like to advise us.

Thanks!

JJ