Other Parts Discussed in Thread: TPA3118D2, TAS5766M

Hello,

Use Case:

PVDD: 25VDC ± 0.25VDC

Output Configuration: PBTL

Rload: 2.7ohms

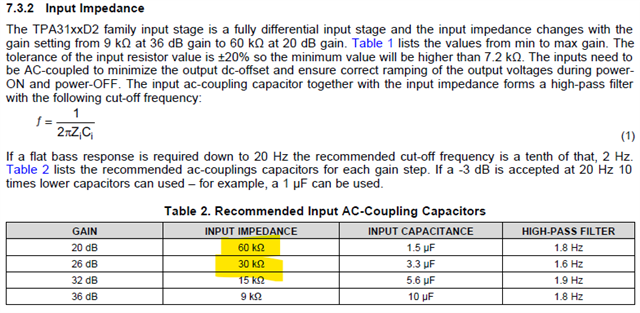

Gain/Switching Frequency: 26dBV, 768kHz

We have a several units of TAS5756M devices who are tripping a DC offset error, due to high leakage on the AC coupling capacitors between the DAC output and the IN+ terminal.

We are consistently seeing trip thresholds much lower than 5VDC. Here is a collection of data that we have taken on several units, from several different lots:

The voltage in the column highlighted was taken on seven different boards and measured differentially from SPK_OUT+ to SPK_OUT- for two TAS5756M ICs on the same board- both of which were configured as per the operating conditions at the top of this post.

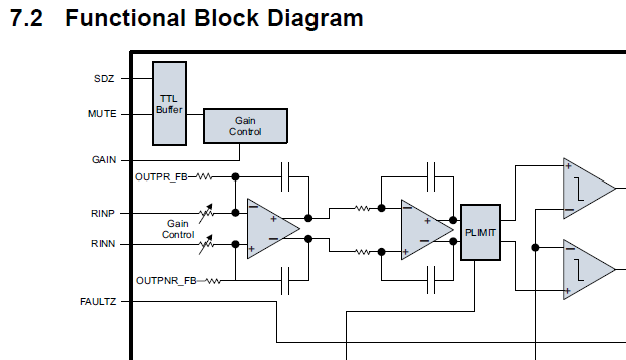

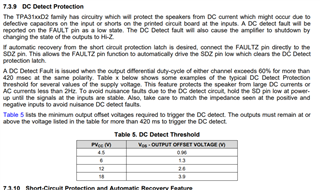

There is no specification for this threshold in the data sheet, and thus we reviewed the TPA3118 data sheet for guidance (since it is very similar to the power stage in the TAS5756M/TAS5766M device). According to the TPA3118D2 data sheet, the value should be over 5VDC, as shown below:

But that is much higher than what we are seeing...

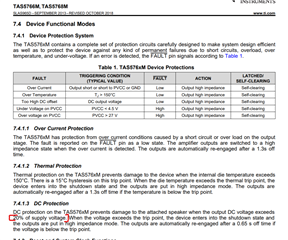

Of course, the TAS5766M device is very similar to the '56M, so we consulted its data sheet as well. It also reports that, since we are using the device at 25VDC on PVDD, we should expect ≈5V of DC offset on the output of the device before tripping a fault:

In further searching we found the popular application note on DC Offset in the TPA31xx family, shown here: https://www.ti.com/lit/an/sloa261/sloa261.pdf

Upon review, this document seems to indicate that the threshold is more like ≈ 2.7VDC

Which is correct, given our operating conditions?

We would also like to know:

- What is the nominal trip threshold, given our operating conditions, that we should expect in room temperature?

- What is the tolerance for this threshold as measured in the characterization or PTE data (or perhaps the design team can offer some insight)?

- Can you please provide min/max data for this parameter from PTE or Char data?

I understand that these values are not published and are not guaranteed, but we are attempting to understand why we are seeing early trip points and need to understand the extent of the issue. It seems that the TPA3118 or the TAS5766 data sheets provide a value which is 1.5x to 2x higher than what we're measuring.

Thanks in advance for your help, and we look forward to hearing from you.

Cody