To Whom It May Concern,

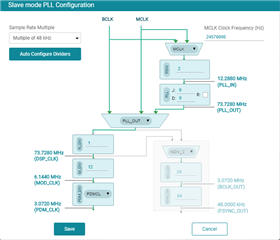

I would like to program the part to use the PLL configuration show below from the PurePath Console. I didn't see the divider register settings in the data sheet, or in the PurePath Console Register Map. What are the registers, register addresses and register settings to implement the diagram? It looks like these registers would be a PLL input select (MCLK or BCLK), PDIV, J,D, N_DIV, M_DIV, and the 3 input clock MUX select feeding N_DIV. In the system I would be supplying a BCLK at 3.0720MHz and FSYNC at 48KHz.

Thanks,

Shawn

P.S. The register's in the data sheet which appear to be relevant are MST_CFG0, MST_CFG1, CLK_SRC, and PDMCLK_CFG. According to the data sheet descriptions most of the settings are not used in slave mode, auto clock configuration disabled, PLL enabled in Auto Clock Configuration.