Hello, I'm developing an acquistion board using the TLV320ADC6120

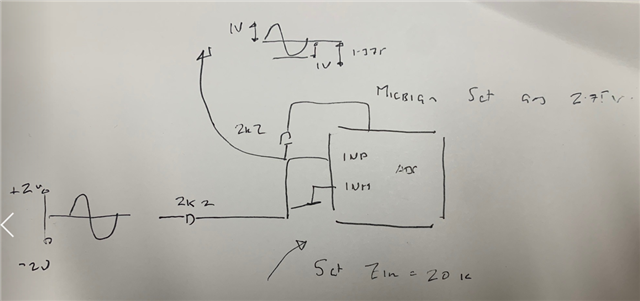

I have an input signal with amplitude +/- 2Vpp cetered at 0V.

I used MICBIAS/2 output to shift the signal to the range 0-2.75V, is it correct to use this output to create the Common mode voltage?

I need to have a DC coupled signal.

I configured the ADC in sigle ended input mode DC coupled. (IN1P, IN1M=GND), is it correct?

The digital signal I acquire seem to be saturated in the upper side, if I configure the channel as DIFFERENTIAL mode I see the aspected output.

I'm also in trouble with configuration register BIAS_CFG Register (Address = 0x3B) what is the meaning of VCM cited in the table 8-84? Can I use MICBIAS with VCM level to shift my signal?