Other Parts Discussed in Thread: ADC6120EVM-PDK

Hi all,

I am following up the related question (sorry for the late feedback).

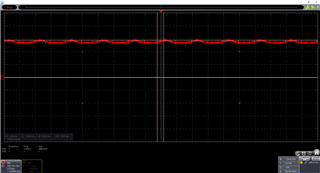

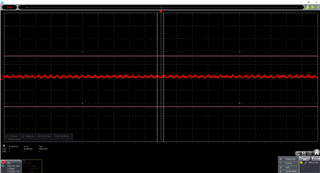

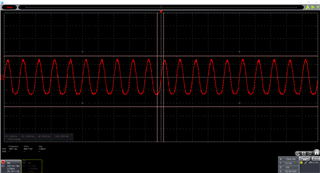

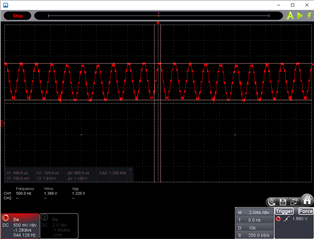

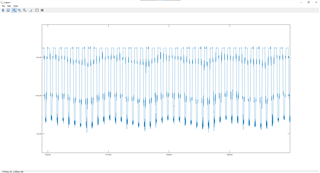

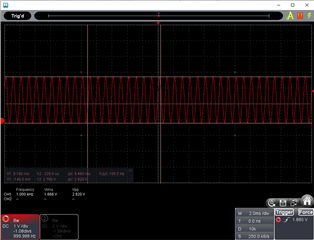

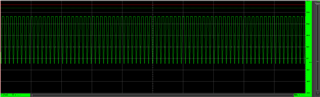

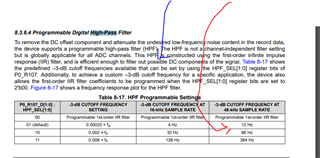

I tried the configuration provided by Sanjay Dixit, and the signal seems to be centered at 0 and not clipped, but looking for the differences with our configuration we find out that there is the high pass filter at 12 Hz enabled, that is not suitable for our application.

Thanks to this test we realized that the ADC is clipping the signal after the filter, is that correct?

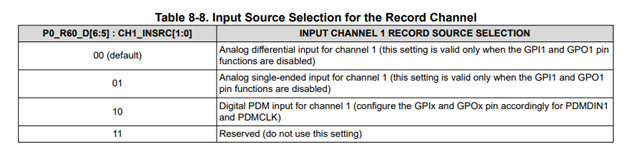

I have another question about the MICBIAS configuration: the configuration MBIAS_VAL = 2 to 4 are descripted in the R59 description but are given as "Reserved (do not use these settings)" in the Programmable Microphone Bias paragraph. Can the configuration "4d = Microphone bias is set to VCM = average of IN1M and IN2M, for ADC single-ended configuration" be a solution for our set-up?

Thanks,

regards

Arianna