Other Parts Discussed in Thread: DIX9211, PCM9211, SRC4192

Hi,

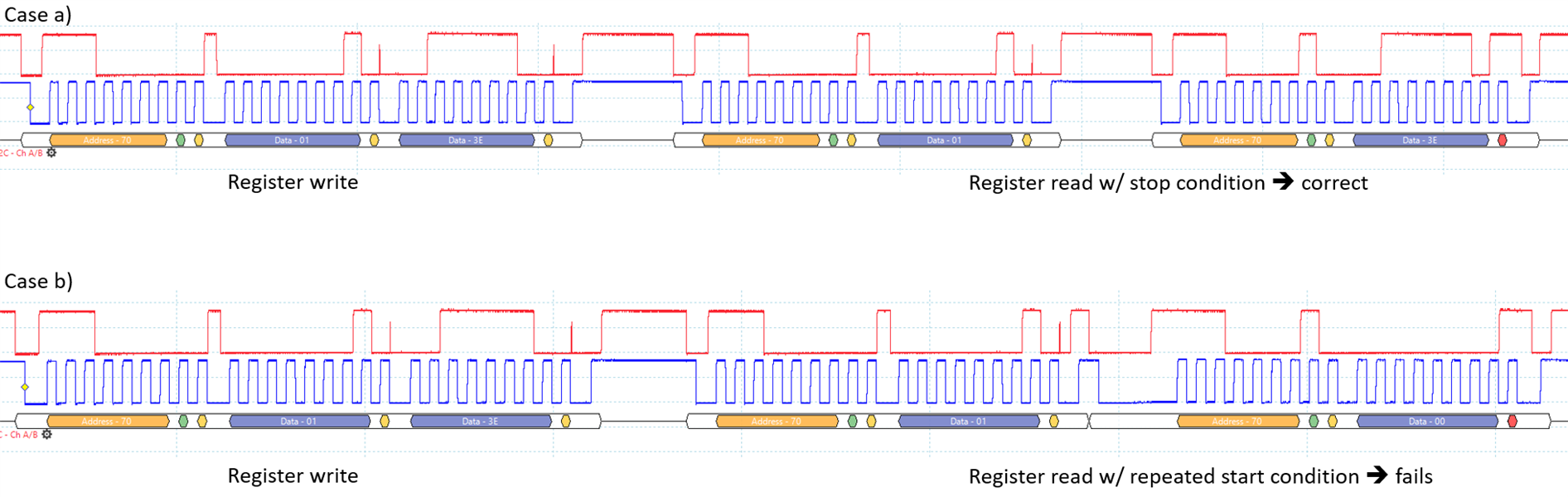

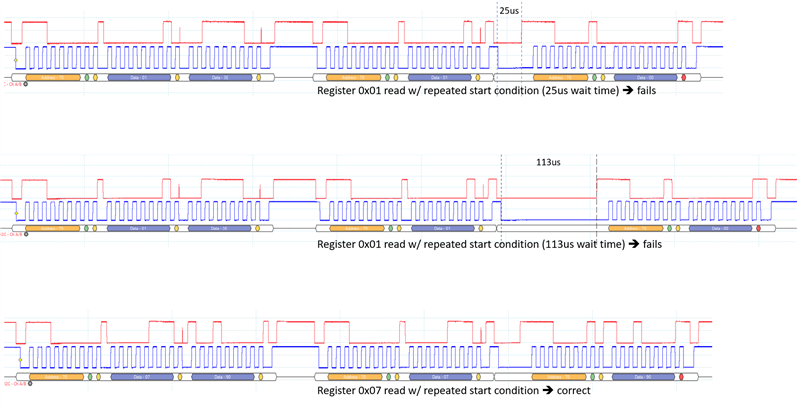

I have observed an unexpected behavior when reading back the control registers via I2C. When I read the registers as suggested in datasheet fig. 22 (b), random read, using a "Repeated Start" condition between address write and data read cycle I can read all registers but the "Power down and Reset" register at address 0x01 which will always return zero. In fact the read to register 0x01 seems to trigger a reset since all other register values I read back after reading 0x01 are zero and the chip is back in default configuration. However, if a Stop condition is used between the address and the data read cycle (according to fig 22, (a), current address read), reading address 0x01 does not trigger a reset and the configuration is kept. Is this expected?

Regards

Hans