Hello,

On the datasheet, Section 7.11 Timing Requirements.

(1) tBCKL min is 1.5x tSCKI.

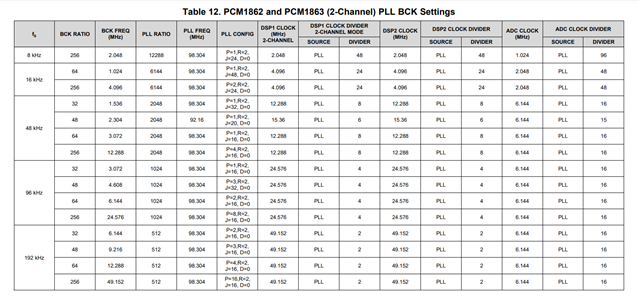

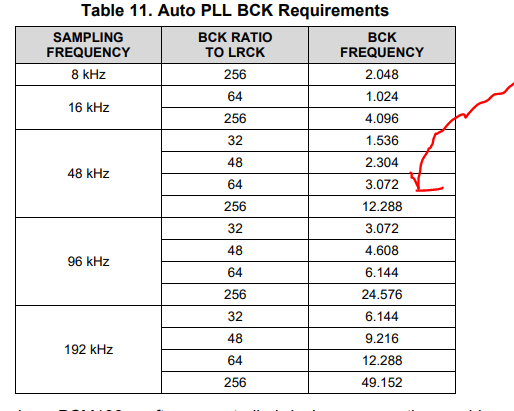

In our customer's usage is I2S slave mode with PLL BCK input.

At this case, SCKI is not used but internal PLL generate SCK.

Should we convert your requirement to 1.5x tSCK?

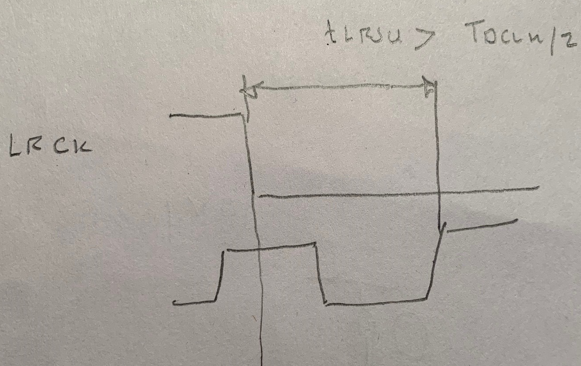

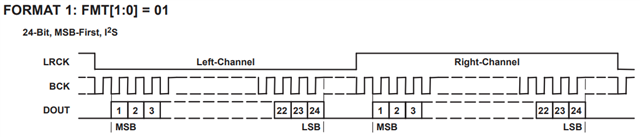

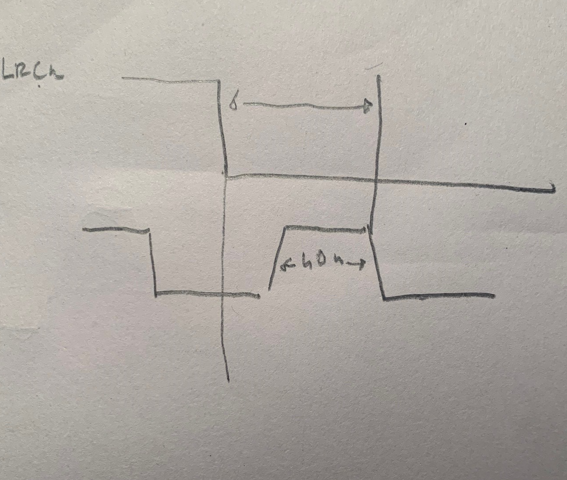

(2) tLRSU min is 50ns.

At 192KHz sampling data, LRCK cycle is 81.4ns and setup time become 40.7ns.

We cannot meet tLRSU requirements, what is reason of this discrepancy.

(3) tLRDO = -10 ~ 40ns

At Fs48KHz 64BCK condition, actual capture of the device output tLRDO is 320ns.

What is reason of this difference?

(4) tLRHD threshold LRCK is 1.4V and BCK is 1.4V

But the drawing of LRCK threshold looks 90% point, which is correct?

Regards,

Mochizuki