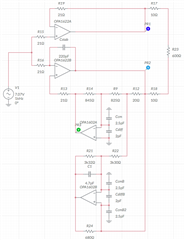

Other Parts Discussed in Thread: LM4562, OPA211, OPA210, THS4031, OPA1612, , OPA828, OPA2210, OPA1637, LME49860, THP210, TINA-TI, OPA1602

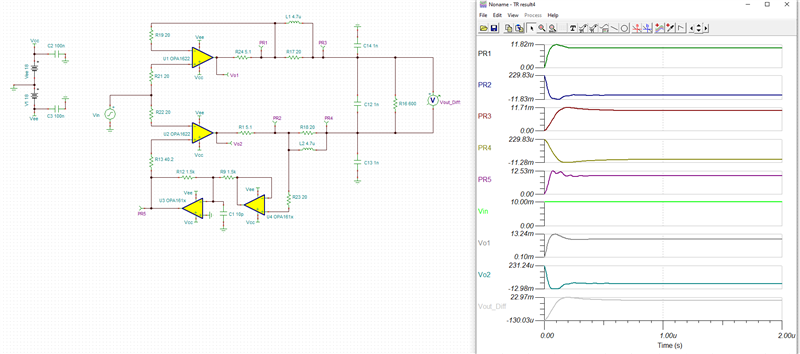

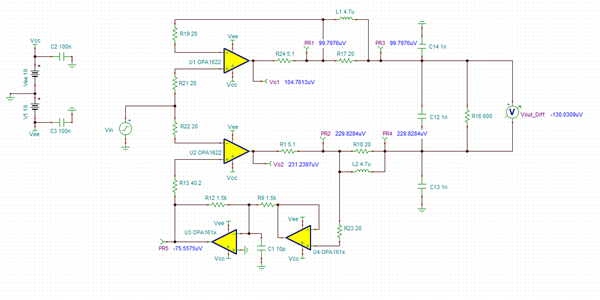

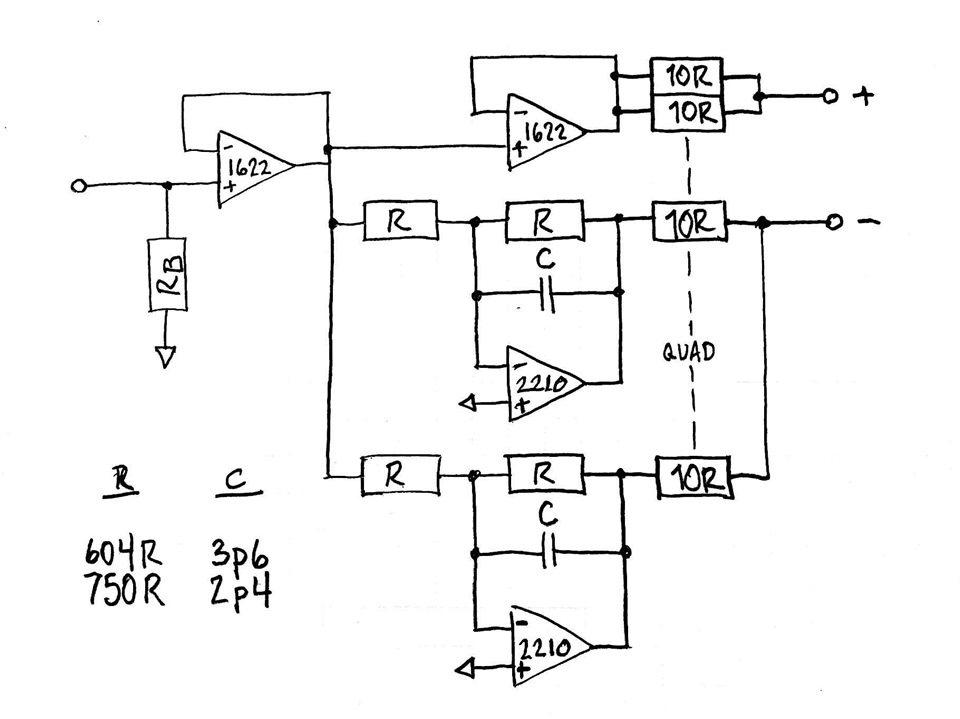

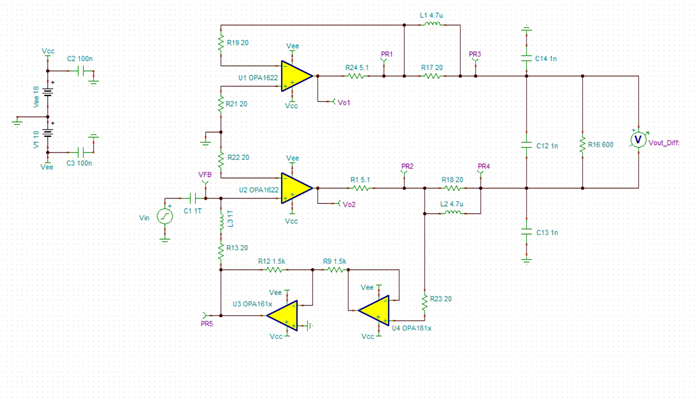

Would this work IRL? Anything to look out for? Suggestions for improvement?

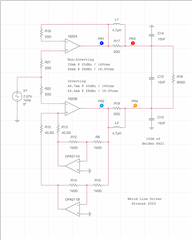

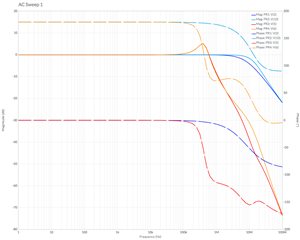

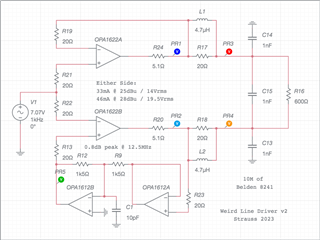

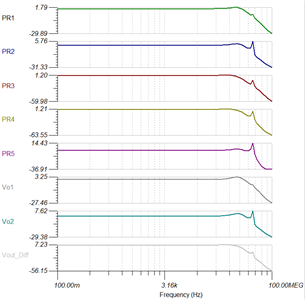

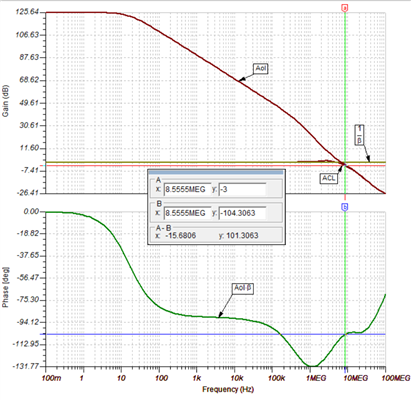

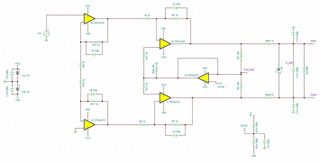

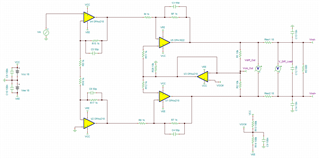

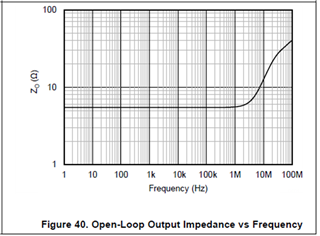

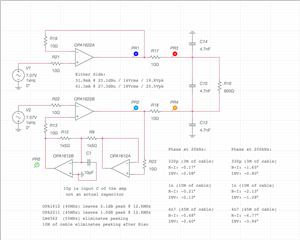

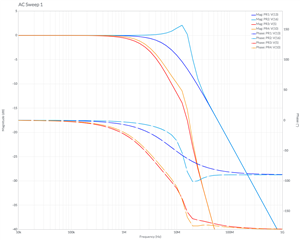

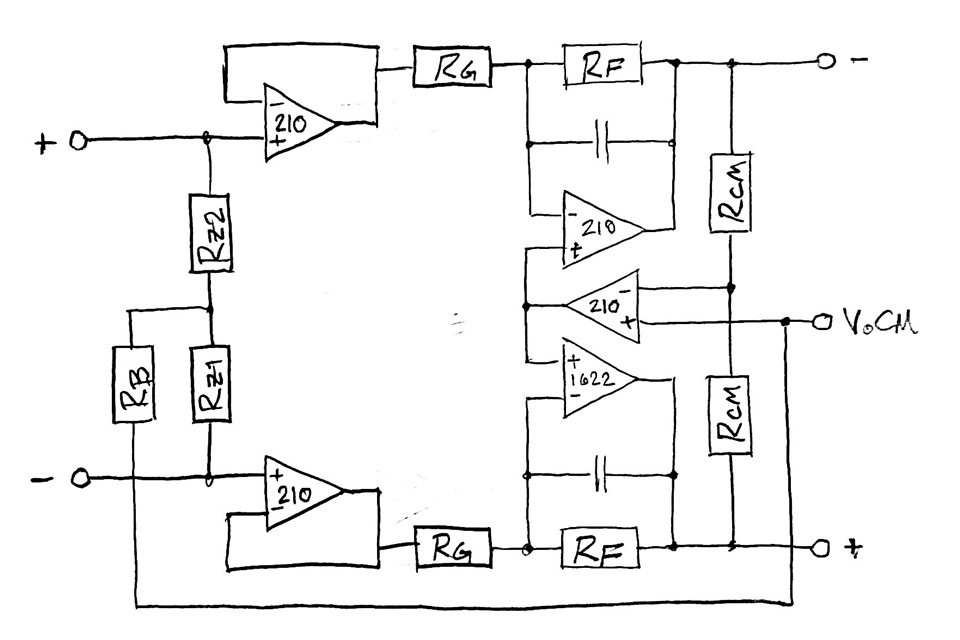

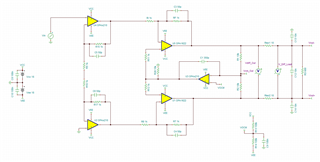

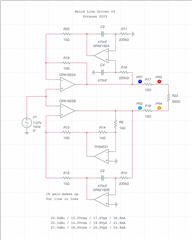

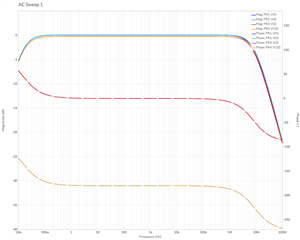

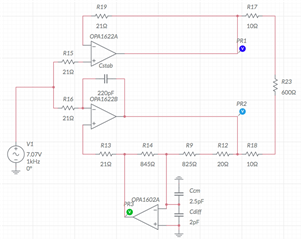

• The ideal amp for the duty the OPA2211 is performing here would run at a minimum of 40MHz, or ≥20MHz at Av=-1. Elimination of inverting 1622 peaking around 8MHz involves running the 2211 without any Cf -- even at Rf=604R and Cf=5p6 there's a 1.7dB peak. Normally the Cf omission would be verboten, but I suspect resultant peaking at the 2211 output might actually be an advantage in this scenario, as it would turn any 1622 peaking down if the peaks were in the same neighborhood. The LM4562 is a little faster and is thus more effective at eliminating 1622 peaking (about 0.8dB vs the 1.7dB I mentioned), but it would limit output capability on ±15V supplies, which this is designed for.

• An alternate method of achieving inverting 1622 flatness involves a composite amp with a single unity inverting OPA211 (with Cf) wrapped around a THS4031 with a little gain to open up the bandwidth. That's perfect, but then it's three packages and 17.3mA Iq, as opposed to this which is two packages and 12.4mA Iq. The Groner/Polak composite does work, but you have to tweak the bandwidth a little wider. I've actually made this work with the much-slower OPA210 wrapped around a THS4031, with no Cf at the 210 and the THS4031 running a little more than Av=2.

• I see from another thread that minimum Riso for the 1612/2211 family is 3R16, and the 1622 input capacitance is super low, so the 40R2 ballast resistors are total overkill. But they're there in case the better choice is an OPA1612, In which case I would need to inject a servo voltage using a 2K Rinj. And it doesn't hurt to put a little equal Rs on all ports of the 1622.

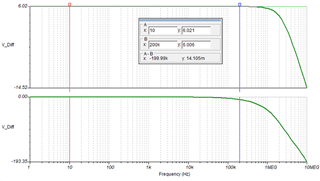

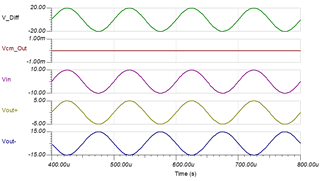

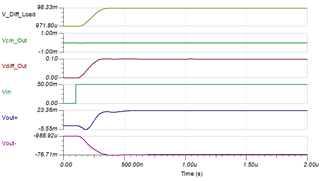

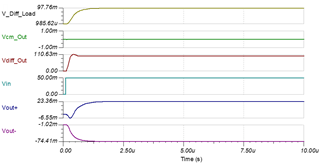

• The inverting side of the 1622 is for sure loaded to the hilt when driving a 600Ω external termination. But I see from the data sheet that it can push 66.6mA cleanly at the next lowest documented headphone load, so I'm wondering what happens at 28dBu differential with one side at ~64mA (phase margin, THD, et al). AFAICT it'll do 25dBu just fine.

• There is no appreciable HF difference between this and a 10K load at the end of that football field of cable length.

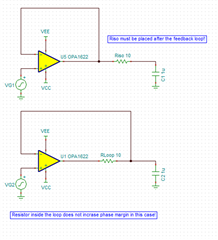

• No output protection drawn, but imagine the typical BAV99s from outputs to rails, and the 20R in the non-inverting 1622s FB loop is a good thing too.

Cheers.