Other Parts Discussed in Thread: PCM3168

Dear

PCM3168A is configured as a TDM8 output, and the LRCKAD and LRCKDA are combined to connect to the LRCK of the main control chip

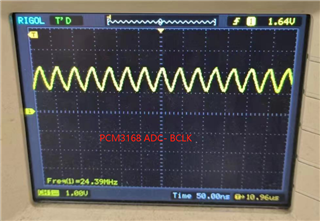

After BCKAD and BCKDA are merged, BCKAD is connected to BCK=12.288M of the main control chip, SPI mode of the main control, PCM3168 as slave, sampling rate LRCK:48K MCLK: 12.88M, BCK: 12.288M;

addr=42, val=0

addr=43, val=0

addr=44, val=0

addr=45, val=0

addr=46, val=0

addr=47, val=ff

addr=48, val=ff

addr=49, val=ff

addr=4a, val=ff

addr=4b, val=ff

addr=4c, val=ff

addr=4d, val=ff

addr=4e, val=ff

addr=4f, val=ff

addr=50, val=1

addr=51, val=6

addr=52, val=0

addr=53, val=0

addr=54, val=0

addr=55, val=0

addr=56, val=0

addr=57, val=0

addr=58, val=d7

addr=59, val=d7

addr=5a, val=d7

addr=5b, val=d7

addr=5c, val=d7

addr=5d, val=d7

addr=5e, val=d7

---readback---:

addr=c0, val=c0

addr=c1, val=6

addr=c2, val=0

addr=c3, val=0

addr=c4, val=0

addr=c5, val=ff

addr=c6, val=0

addr=c7, val=ff

addr=c8, val=ff

addr=c9, val=ff

addr=ca, val=ff

addr=cb, val=ff

addr=cc, val=ff

addr=cd, val=ff

addr=ce, val=ff

addr=cf, val=ff

addr=d0, val=1

addr=d1, val=6

addr=d2, val=0

addr=d3, val=0

addr=d4, val=0

addr=d5, val=0

addr=d6, val=0

addr=d7, val=0

addr=d8, val=d7

addr=d9, val=d7

addr=da, val=d7

addr=db, val=d7

addr=dc, val=d7

addr=dd, val=d7

addr=de, val=d7

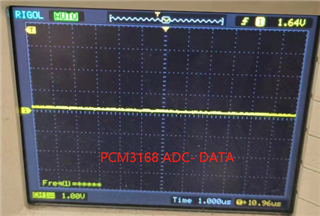

The output of 48K slave mode of TDM8 is normal. After the sampling rate is 96K, the output of single rate, double rate and automatic rate is abnormal. Please help to check the configuration of the 96K which needs to be changed, thank you! When configured in dua rate or auto mode, ADC DATA does not generate waveform; when configured in single rate, there is noise

hi Andrew It is 100MHz

hi Andrew It is 100MHz