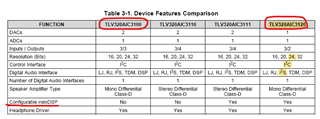

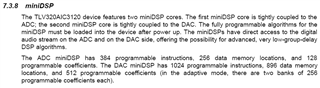

Other Parts Discussed in Thread: TLV320AIC3111, TLV320AIC3100

I am trying to set it up like this.

External input operates as I2S stream in FPGA.

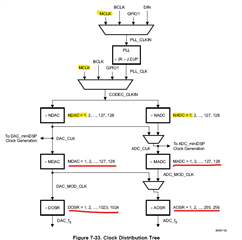

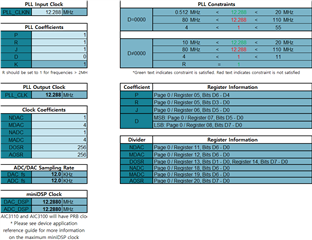

MCLK=12.288Mhz, ADC/DAC=12khz

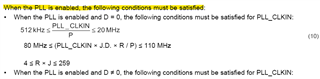

1) not to use PLL. Then, can I ignore the PLL constraint?

Can I use the settings below?

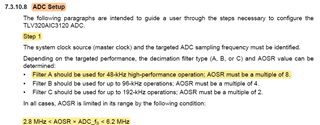

NADC : 1 / MADC : 4 / AOSR : 256 / ADC_fs : 12 khz

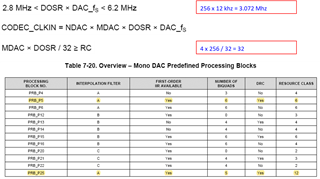

NDAC : 1 / MDAC : 4 / AOSR : 256 / DAC_fs : 12 khz

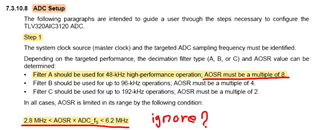

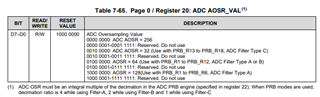

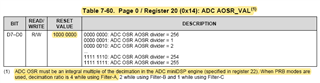

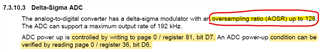

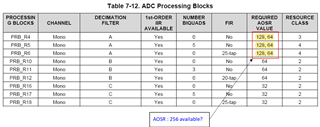

2) AOSR : 256, is it possible?

2.8Mhz <= AOSR x ADC_fs <= 6.2Mhz

Therefore, the AOSR should be 256.

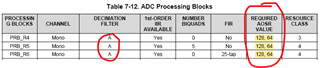

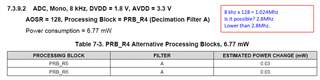

3) I want to use PRB_R4, R5, R6. Doesn't AOSR have to be 128? Can I use 256?

4) PRB_R25, P5 with DRC function will be used.

Can I use the settings above?

The FPGA's IP is configured for I2S communication at 256 times Fs.

So it would be nice to operate with the set clock. Is it possible to use it with the above setting?

If there are other better settings, please correct me.