Hi,

Our customer inquired about SCKI's jitter tolerance range.

According to the datasheet

”For changes less than ±5 BCK, resynchronization does not occur and the previously described digital output control and discontinuity do not occur.”

I can read that the tolerance range is ±5 BCK or less, but is this correct?

However, if the allowable range of jitter is 5BCK (BCKP?)

Since 1BCKP=1/(64 fS), it seems like a fairly large jitter.

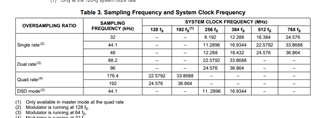

The customer uses a 24MHz system clock, could you help me understand the acceptable range of jitter?

Best regards,

Hiroshi