We are bench testing our custom TAS6422-Q1 board. We are doing power / heat tests by playing 1KHz sine waves via TDM, with the amp outputs connected to 100w 4R resistors.

At lower amp gains everything is good, we get an excellent low distortion sine wave at the amp outputs. However, once we go above about ~25w output power (about -2.5dB @ gain 4 it seems), the output starts rapidly and randomly "muting" or silencing (see attached image). This happens one or time times a second usually, for just very brief moments (a few tens of milliseconds).

Note we have the other channel at -9dB, and are only monitoring one channel for now. Both channels have 4R loads attached. Temperatures are all good (40-50C), the part is well heatsunk.

Here's the thing: We are monitoring all the amp diagnostics registers, and we see no alarms. Power rails appear to be good, although we will 'scope those tomorrow to double check. We have other items on the same power rails (eg; the MCU generating the TDM), and that exhibits no issues. We have tried 2 different power supplies, both of which are >8A. Current draw is around 2A @ 24v.

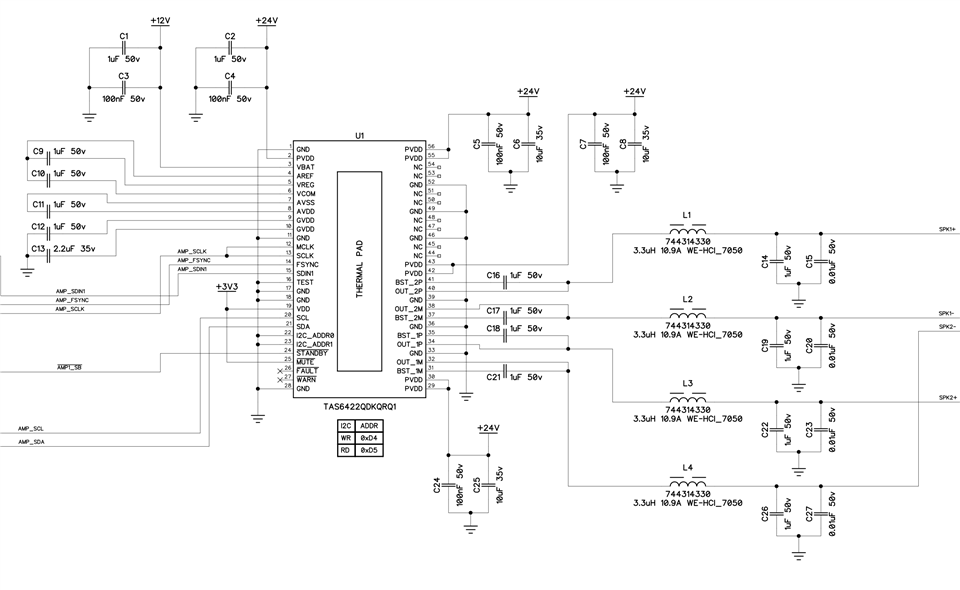

I have attached our schematic which should explain the design. Is there anything we're doing wrong? Much appreciate any help. We will work on this again tomorrow, and update if we find anything interesting.