Other Parts Discussed in Thread: TAS2781,

Tool/software:

Hi,

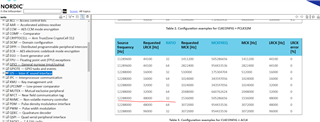

Im preparing the interfacing of I2S to this nordic micro nrf5340 to the TAS2781 evm. at this moment I can only configure the micro I2S with the frame and sbclk below scope format.

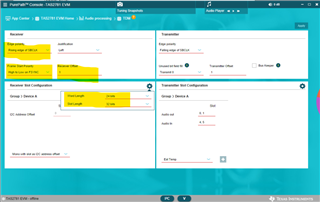

Now, if I hook up my scope with just the 2781evm, the xmos channel i2S is default configured to TDM, where the frame signal inhibit for one sbclk cycle at the start of the comms only and at the end of the last bit depending on the channel number. I was trying to find a way to configure xmos to communicate similar to my micro that I intend to use but with no success.

my question are

- does the tas2781 would be compatible with the i2S format scope capture below? I have attached a section in the datasheet that it should be possible but I just want to confirm as I didn't see any setting in the PPC3 control panel to make this I2S configuration.

- can I change xmos TDM format to be similar to the waveform below?. This way I can iterate on the correct configuration using the EVM and PPC3 and do an extract of the final i2C config header file to be used in my code.?\

Note: at this moment I have just hook up the i2c line of my micro to the 2781(working fine), Once I hook up the i2S between the boards, i will loose the PPC3 interaction with the 2781evm. which will make this thing difficult to debug..