Tool/software:

Hi team,

Customer met some problems for PCM6260-Q1. You can find the details as below. Please help provide some suggestions.

Besides, do we have purepath tool that can help on this debugging? I shared this one(https://www.ti.com.cn/tool/cn/PUREPATHCONSOLE) with customer, but their feedback is this can only use with our EVM.

Test setup:

MIC IN(open, not connect Mic) => PCM6260 => Audio DSP => SoC

Test procedure:

12V battery is connected to VBAT_IN -> pull SHDNZ up -> register initialization -> enable ADC and output TDM to Audio DSP -> pull SHDNZ low to high -> register initialization -> enable ADC and output TDM to Audio DSP

Phenomenon:

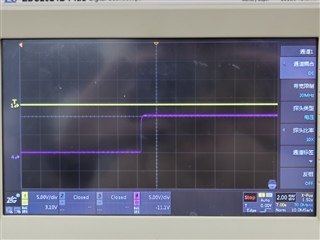

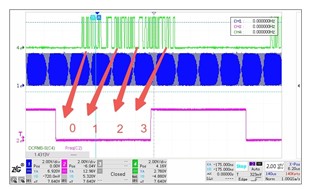

Recording data is abnormal. It has reproduced 5 times. You can find the waveform and schematic as below.

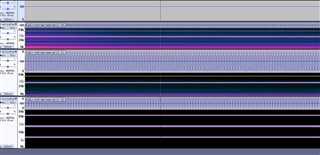

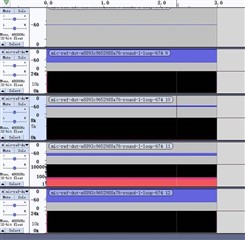

Waveform: (CH1: BCLK CH2: LRCK CH4: DATA)

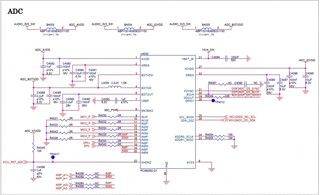

Schematic:

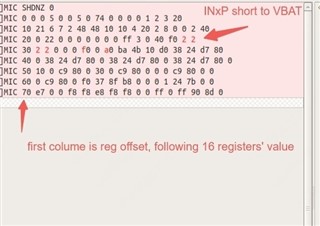

Data:

Phenomenon 1: DC signal captured when abnormal(reproduced twice)

Phenomenon 2: looks like some specific frequency point noise(reproduced once)

Phenomenon 3: noise(reproduced once)

Thanks!

Ethan Wen