This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi, Ok Hwan,

Someone will be getting back to you tomorrow.

-d2

Hi, Tuan

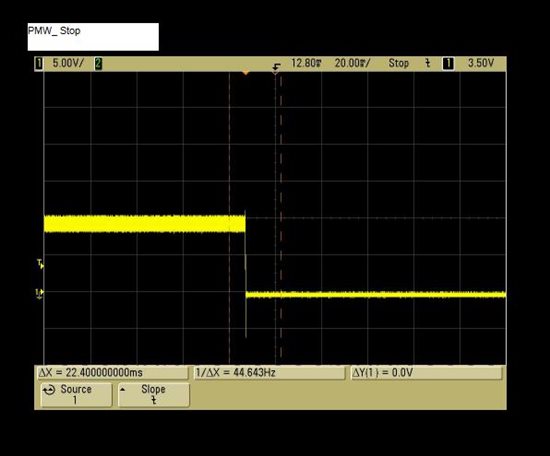

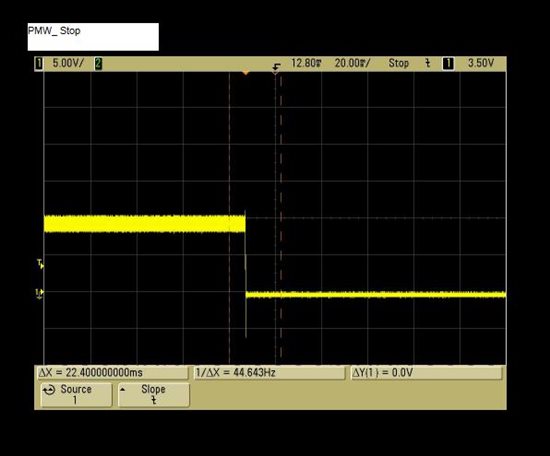

When i set 0x03 bit D2 as 1 to disable PWM soft start, PWM stop works well as doing not soft start.

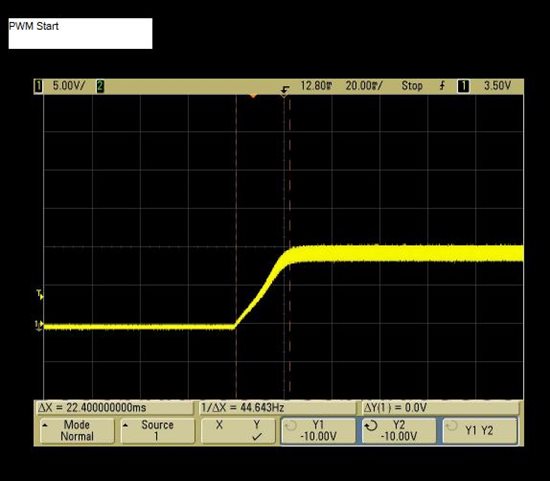

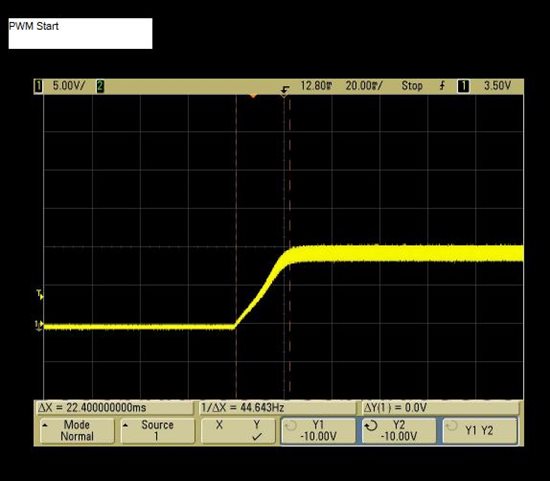

But PWM start still remains soft start.

I want to make soft start fixed 'disable' to clear POP noise.

Problem is POP noise, If you have any idea to remove POP noise pls advise me.

Thanks,

Hello Ok:

Please try the following steps and see if they help.

1) Hold all logic inputs low. Power up AVDD/DVDD and wait for

them to settle in the allowed range

2) Drive PDNZ=1, MUTEZ=1, and drive other logic inputs to the

desired state.

3) Provide a stable MCLK, LRCLK, and SCLK

(Clock errors must be avoided during the init sequence)

4) After completing step 3, wait 100us and then drive RESETZ high

and wait 13.5ms after RESETZ goes high

5) Trim internal oscillator (write 0x00 to register 0x1B)

6) Wait 50ms while part acquires lock

7) Configure the DAP via I2C, e.g.:

Downmix control (0x21)

Biquads (0x23-0x24 and 0x29-0x38)

DRC parameters and controls (0x3A-46)

Bank select (0x50)

8) Exit all-channel shutdown (write 0 to bit 6 of register 0x05) 9) This completes the initialization sequence. From this point on, no further actions are required on PDNZ, MUTEZ, and clocks. 10) During normal operation the user may do the following: a) Write to Master or individual channel volume registers. b) Write to the Soft Mute register. c) Write to the clock and serial data interface format registers (in manual clock mode only). d) Write to bit 6 of register 0x05 to enter/exit all-channel shutdown. No other bits of register 0x05 may be altered. After issuing the all-channel shutdown command, no further I2C transactions, which address this device, are allowed for a period of at least: 1ms + 1.3*(period specified in start/stop register 0x1A) e) PDNZ may be asserted (low) at any time. Once PDNZ is asserted no I2C transactions, which address this device, may be issued until PDNZ has been deasserted and the part has returned to active mode. Best regards, Tuan