Hi,

Can you explain about Frame slip error ERROR STATUS REGISTER (0x02)?

How to fixe this issue?

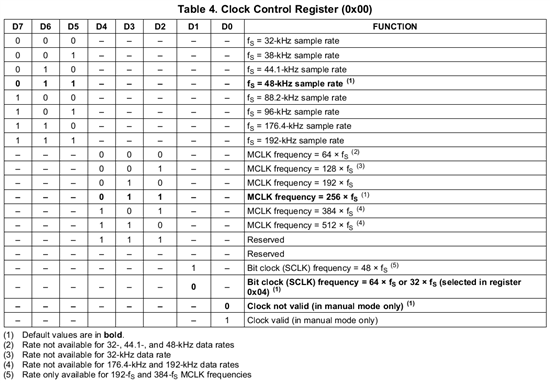

MCLK = 64 * fs is valid for 48000 sampling frequency? If it is true then what about MCLK limit mentioned in TAS5706B data sheet?

Data sheet page number 7

"MCLK is the clock master input. The input frequency of this clock can range from 4.9 MHz to 49 MHz"

Saurabh.