Hello Team,

I'd like to ask you about LM4952.

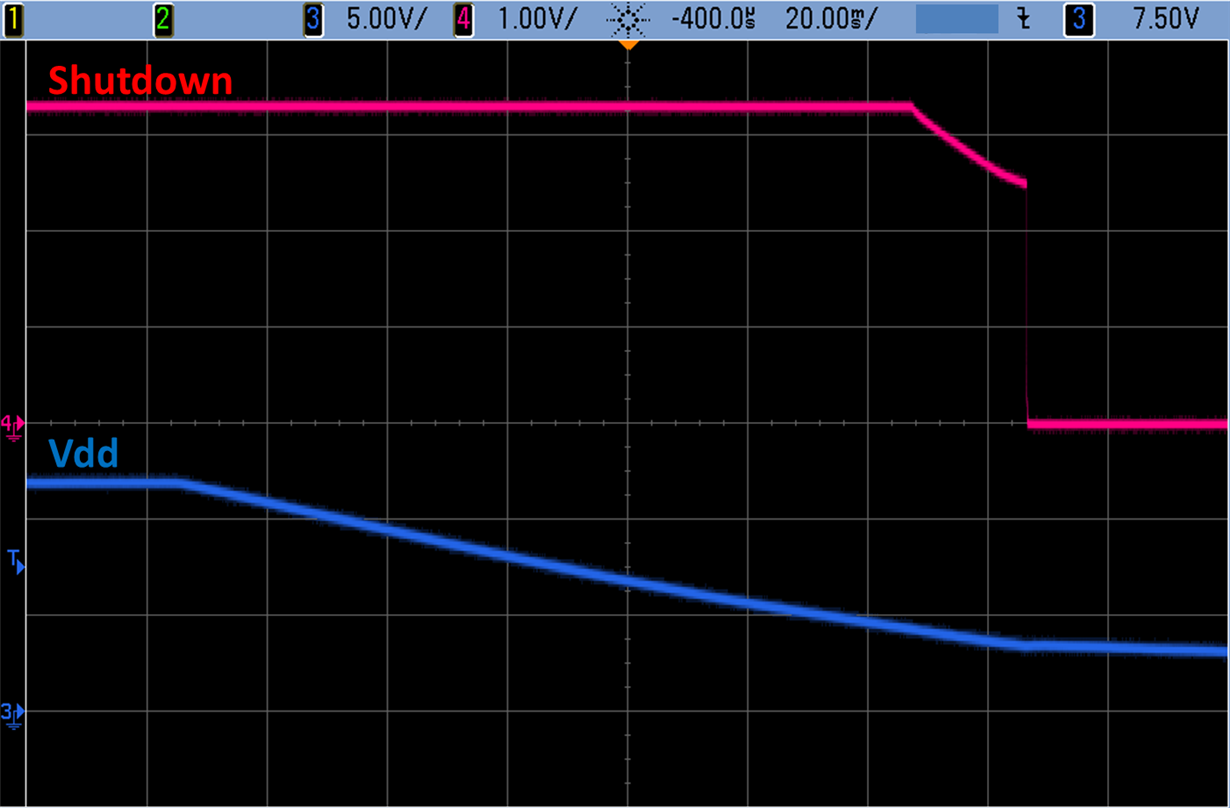

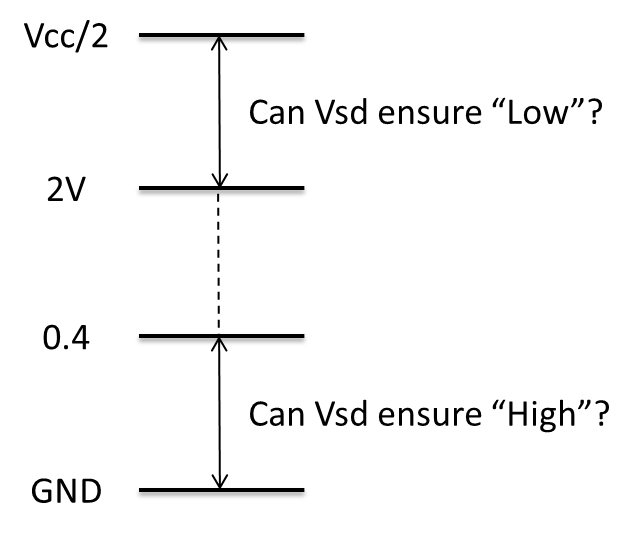

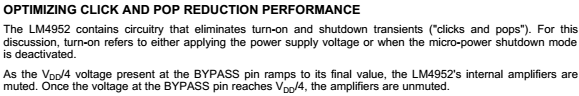

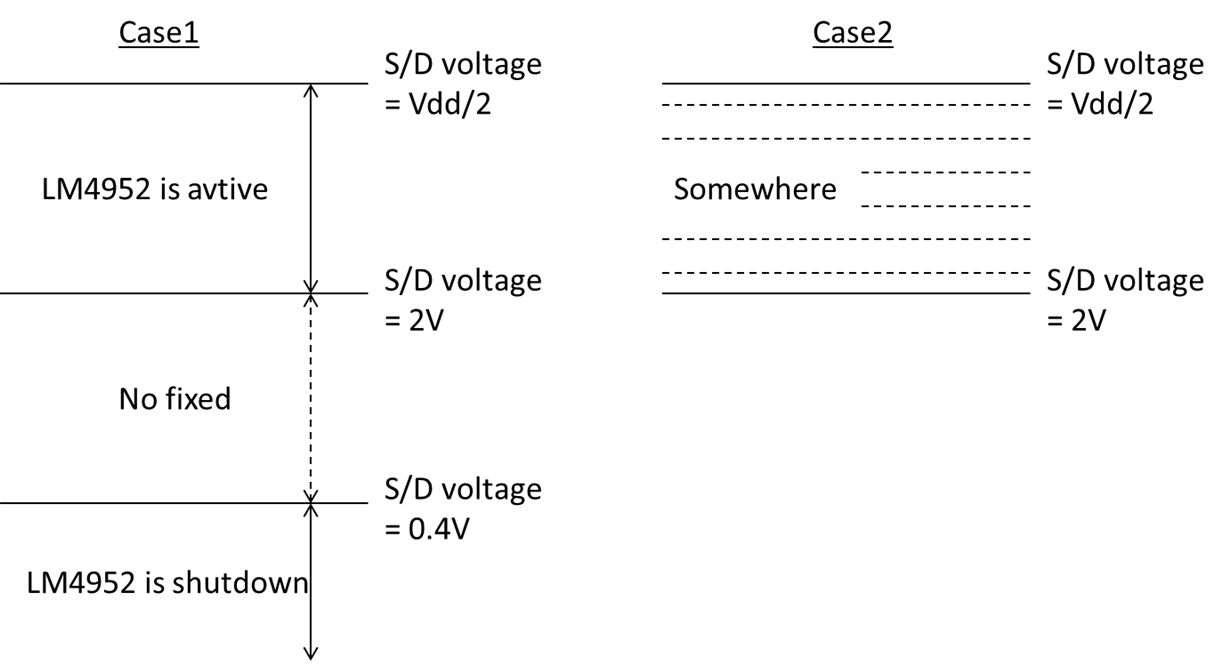

LM4952 can't output audio for a few minutes if LM4952 immediately restarts after power-off.

However LM4952 can output audio if LM4952 restarts after a few minutes from power-off.

Could you tell me the conceivable causes for that?

I think the decreasing Vdd gradually when power-off is the reason.

Best Regards,

Hidetoshi Matsunami