Hello,

I would like to control a SRC4392EVM-PDK by a MSP432-P401R. I use I2C to write to registers. I checked it with a logic analyzer and it is working.

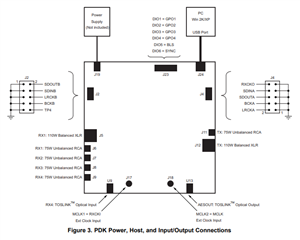

Now I want to route the following signal: I2S --> Port_A_IN --> DIT --> tx_OUT (like shown in the below picture):

I did write to the following registers:

Register Data

0x01 0x40 RESET (I built in a delay after the reset command)

0x01 0x34 I would like to only use the used blocks (Port_A , TX) - Can PDALL bit be neglected?

0x03 0x01 Input Signal of I2S shall be in Slave Mode

(0x04 0x01 - not needed, since Port_A is in Slave Mode)

0x07 0x10 MCLK Input, Clock Divider 256, Port_A as Input

Do I need to read/write to each register that the default values are valid? I already saw in some of the forum replies here that the registers are initialized with 0x00.

Port_A of the SRC4392EVM-PDK is now connected to the output of a Audio Precision 2722:

BITCLK to BLCLK

FRAMECLK to LRCKLA

DATA_Out to SDINA

MASTERCLK to MCLK2=MCLK

The input of Audio Precision 2722 is connected to TC Out of the SRC4392EVM-PDK.

When I now generate a 24 bit 48kHz I2S signal with the Audio Precision and supply into the SRC4392EVM-PDK, I do not see the signal on TX output, flowing back to the Audio Precision.

I already tried some configuration examples from the forum, but nothing worked so far.

Do I have maybe any misinterpretation in my setup?

Hope you can give me some advise and support.

Thanks and best regards,

Michael