Hi,

We want to use TI CODEC chipset TLV320AIC3204 in our two-way radio product.

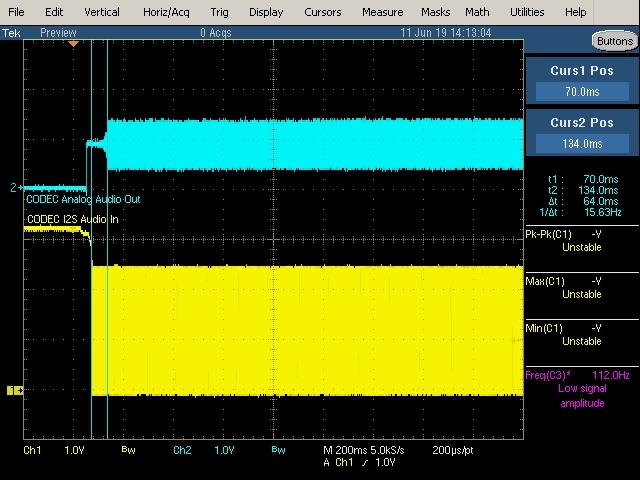

But we found that the delay between receiving I2S signal and outputting analog audio signal is about 64ms.

Is it reasonable? What is the delay specification of this chipset?

The attached image file was got from telescope.

The test procedure is: MCU played a 1KHz tone voice. Use a telescope to measure the CODEC BCLK and CODEC HPR.

Best Regards,

Wells