Other Parts Discussed in Thread: TLV320ADC3101,

Hi guys.

The sound quality of the recording on my board is poor. I hope you can help me see some of the reasons.

My configuration is as flows:

1. use INL2L&IN3L IN2R&IN3R as Differential Pair, But the actual circuit is a pseudo-differential;

2. MCLK pin is connected to BCLK, so MCLK's frequency is equal to BCLK's frequency;

3. use I2S mode, sample rate(48000), wordlength(16bit);

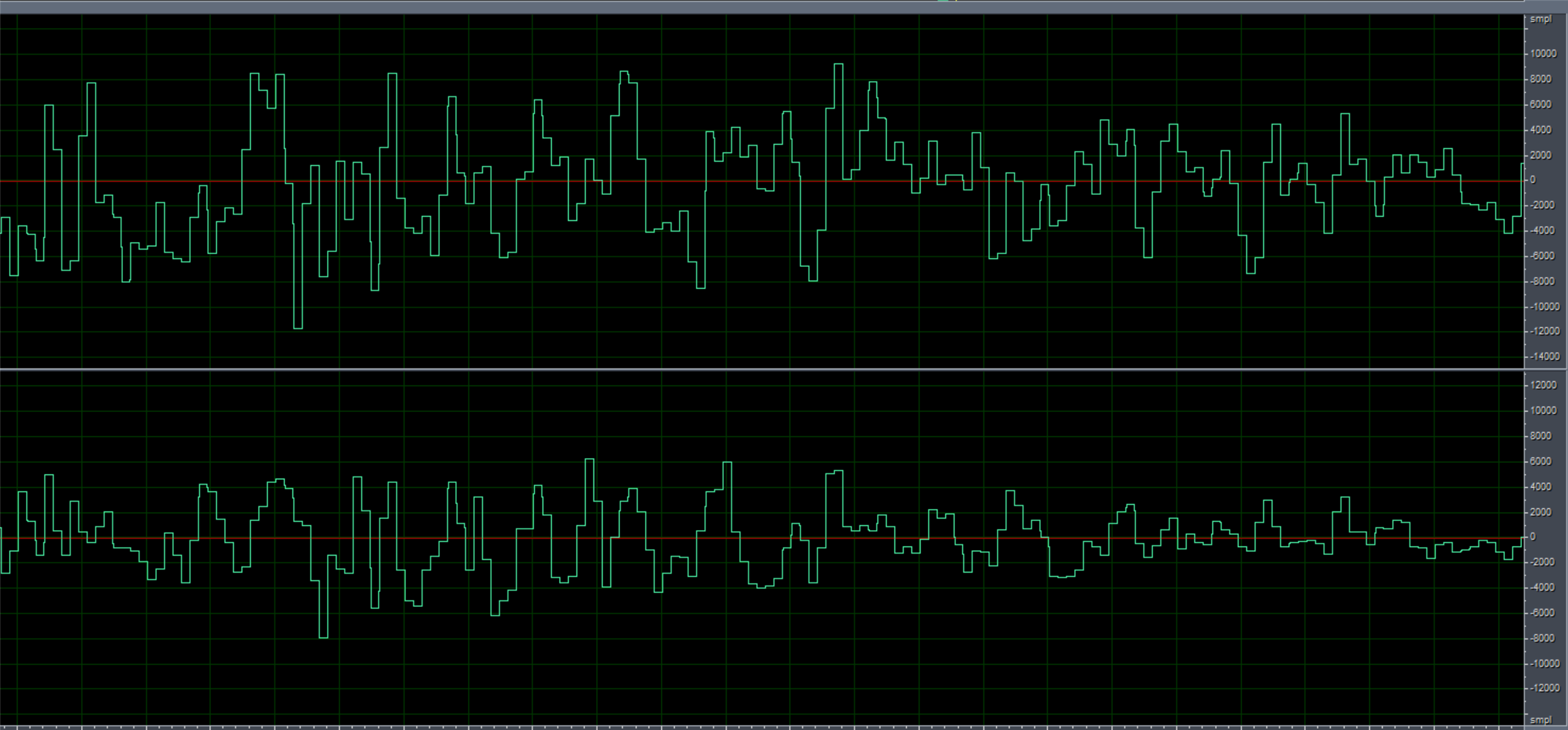

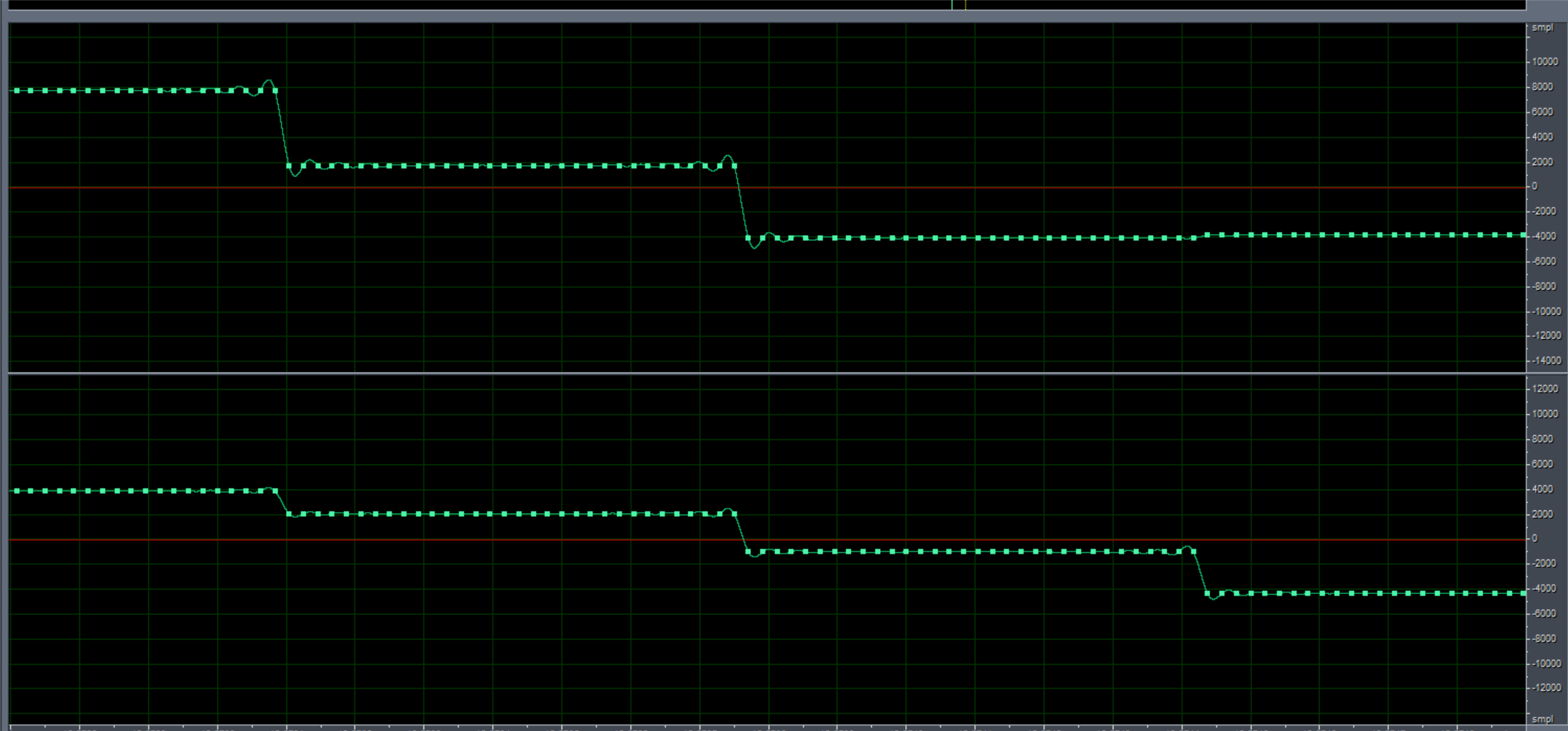

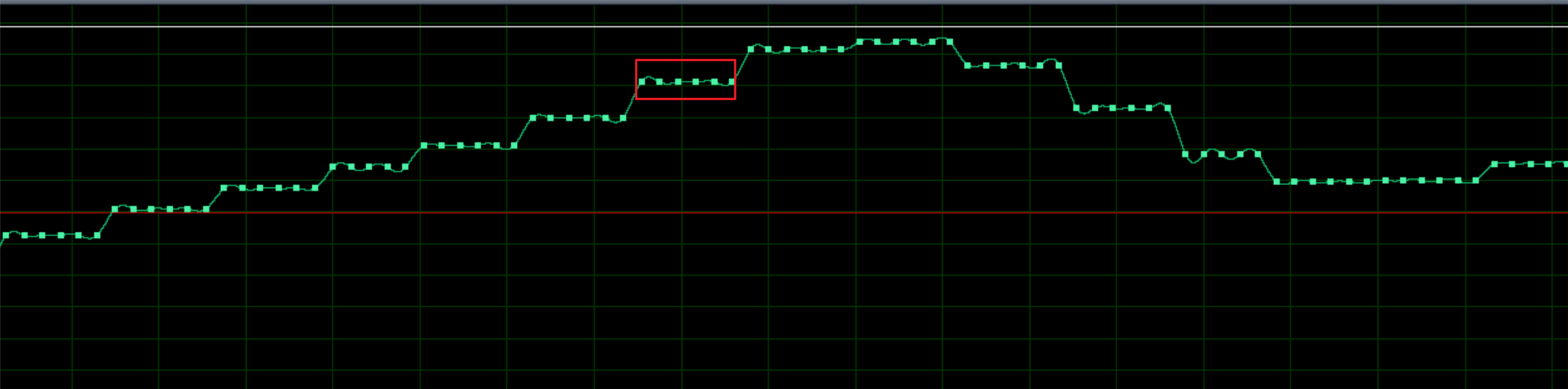

The wavefroms is as flows:

You can see that every 32 sample points will be the same range, which is very strange, and I hope you can give me some Suggestions