Other Parts Discussed in Thread: AM5716

Hi,

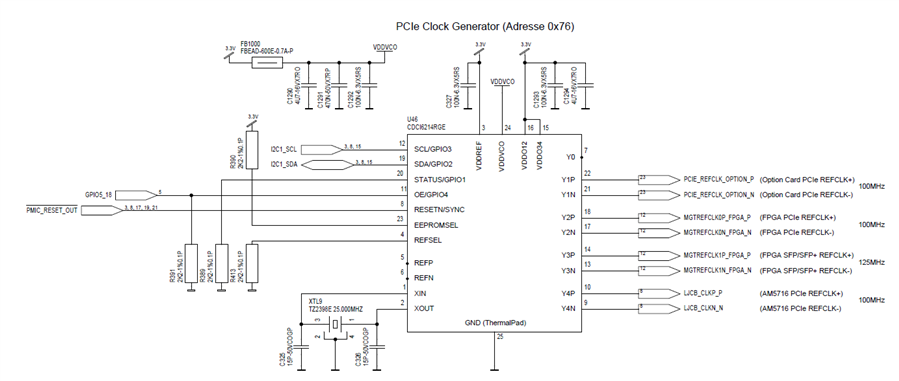

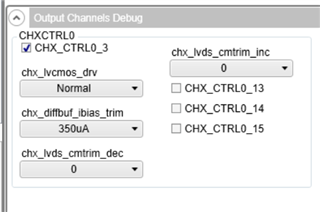

We have problems with some CDCI6214 in our products. On some devices output VOD is far less than the value from the datasheet. We use LVDS output. VDDIO12 and VDDIO34 is 3.3V.

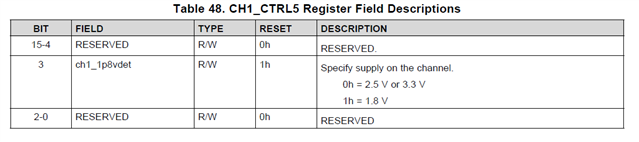

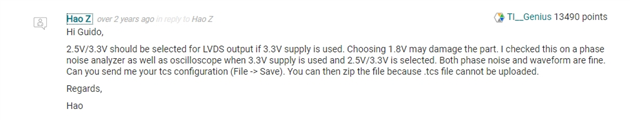

Prior to be more specific to the problem I want to have a clarification on the chX_1p8vdet setting. Some time ago I asked E2E if there is a risk of device damage when selecting EEPROM page 1 (with chX_1p8vdet set to 1) while having VDDIO12 and VDDIO34 at 3.3V. The answer was:

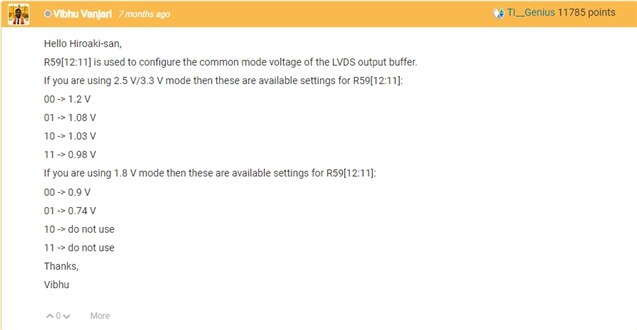

On an other E2E thread I can see that:

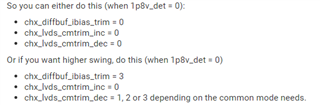

Or that:

Can someone from TI please clarify the situation and tell me what exactly the chX_1p8vdet setting does. If there is a potential risk of a device damage it would be very helpful if this topic is described in more detail in the datasheet.

Thanks and best regards,

Patrick